要想造个芯片, 首先, 你得画出来一个长这样的玩意儿给Foundry (外包的晶圆制造公司)

在 IC 设计中,逻辑合成这个步骤便是将确定无误的 HDL code,放入电子设计自动化工具(EDA tool),让电脑将 HDL code 转换成逻辑电路,产生如下的电路图。之后,反覆的确定此逻辑闸设计图是否符合规格并修改,直到功能正确为止。

控制单元合成后的结果

最后,将合成完的程式码再放入另一套 EDA tool,进行电路布局与绕线(Place And Route)。在经过不断的检测后,便会形成如下的电路图。图中可以看到蓝、红、绿、黄等不同颜色,每种不同的颜色就代表着一张光罩。

完成电路布局与绕线的结果

然后Foundry是怎么做的呢?大体上分为以下几步:

首先搞到一块圆圆的硅晶圆, (就是一大块晶体硅, 打磨的很光滑, 一般是圆的)

此处重新排版, 图片按照生产步骤排列. 但是步骤总结单独写出.

1. 湿洗(用各种试剂保持硅晶圆表面没有杂质)

2. 光刻(用紫外线透过蒙版照射硅晶圆, 被照到的地方就会容易被洗掉, 没被照到的地方就保持原样. 于是就可以在硅晶圆上面刻出想要的图案. 注意, 此时还没有加入杂质, 依然是一个硅晶圆. )

3. 离子注入(在硅晶圆不同的位置加入不同的杂质, 不同杂质根据浓度/位置的不同就组成了场效应管.)

4.1干蚀刻(之前用光刻出来的形状有许多其实不是我们需要的,而是为了离子注入而蚀刻的. 现在就要用等离子体把他们洗掉, 或者是一些第一步光刻先不需要刻出来的结构, 这一步进行蚀刻).

4.2湿蚀刻(进一步洗掉, 但是用的是试剂, 所以叫湿蚀刻).

--- 以上步骤完成后, 场效应管就已经被做出来啦~ 但是以上步骤一般都不止做一次, 很可能需要反反复复的做, 以达到要求. ---

5 等离子冲洗(用较弱的等离子束轰击整个芯片)

6 热处理,其中又分为:

6.1 快速热退火(就是瞬间把整个片子通过大功率灯啥的照到1200摄氏度以上, 然后慢慢地冷却下来, 为了使得注入的离子能更好的被启动以及热氧化)6.2 退火6.3 热氧化(制造出二氧化硅, 也即场效应管的栅极(gate) )

7 化学气相淀积(CVD), 进一步精细处理表面的各种物质

8 物理气相淀积(PVD), 类似, 而且可以给敏感部件加coating

9 分子束外延 (MBE)如果需要长单晶的话就需要这个..

10 电镀处理

11 化学/机械 表面处理

然后芯片就差不多了,接下来还要:12 晶圆测试13 晶圆打磨

就可以出厂封装了.

我们来一步步看:

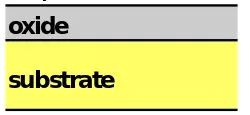

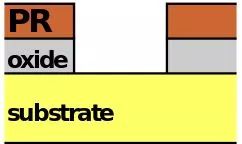

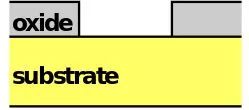

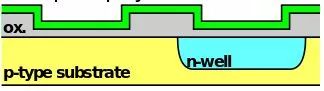

1上面是氧化层, 下面是衬底(硅) -- 湿洗

2 一般来说, 先对整个衬底注入少量(10^10 ~ 10^13 / cm^3) 的P型物质(最外层少一个电子), 作为衬底 -- 离子注入

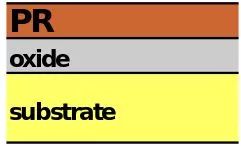

3先加入Photo-resist, 保护住不想被蚀刻的地方 -- 光刻

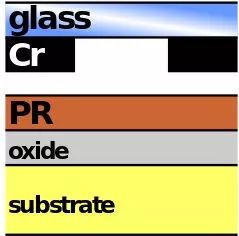

4.上掩膜!(就是那个标注Cr的地方.中间空的表示没有遮盖,黑的表示遮住了.)-- 光刻

5 紫外线照上去... 下面被照得那一块就被反应了-- 光刻

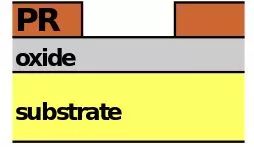

6.撤去掩膜.-- 光刻

7 把暴露出来的氧化层洗掉, 露出硅层(就可以注入离子了)-- 光刻

8 把保护层撤去. 这样就得到了一个准备注入的硅片. 这一步会反复在硅片上进行(几十次甚至上百次). -- 光刻

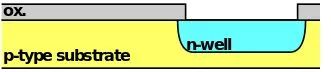

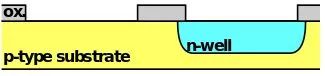

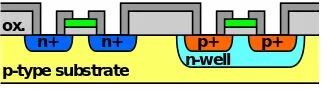

9 然后光刻完毕后, 往里面狠狠地插入一块少量(10^14 ~ 10^16 /cm^3) 注入的N型物质就做成了一个N-well (N-井) -- 离子注入

10 用干蚀刻把需要P-well的地方也蚀刻出来. 也可以再次使用光刻刻出来. -- 干蚀刻

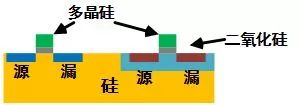

11 上图将P-型半导体上部再次氧化出一层薄薄的二氧化硅. -- 热处理

12 用分子束外延处理长出的一层多晶硅, 该层可导电 -- 分子束外延

13 进一步的蚀刻, 做出精细的结构. (在退火以及部分CVD) -- 重复3-8光刻 + 湿蚀刻

14 再次狠狠地插入大量(10^18 ~ 10^20 / cm^3) 注入的P/N型物质, 此时注意MOSFET已经基本成型. -- 离子注入

15 用气相积淀 形成的氮化物层 -- 化学气相积淀

16 将氮化物蚀刻出沟道 -- 光刻 + 湿蚀刻

17 物理气相积淀长出 金属层 -- 物理气相积淀

18 将多余金属层蚀刻. 光刻 + 湿蚀刻

最开始那个芯片, 大小大约是1.5mm x 0.8mm

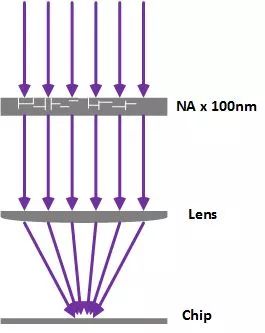

比如说我们要做一个100nm的门电路(90nmtechnology),那么实际上是这样的:

这层掩膜是第一层, 大概是10倍左右的Die Size

有两种方法制作:EmulsionMask和MetalMask

EmulsionMask:

这货分辨率可以达到 2000line / mm (其实挺差劲的... 所以sub-micron ,也即um级别以下的 VLSI不用... )

制作方法:首先:需要在Rubylith(不会翻译...)上面刻出一个比想要的掩膜大个20倍的形状(大概是真正制作尺寸的200倍),这个形状就可以用激光什么的刻出来,只需要微米级别的刻度.

然后:

给!它!照!相!,相片就是EmulsionMask!

如果要拍的"照片"太大, 也有分区域照的方法.

MetalMask:

制作过程:1.先做一个EmulsionMask,然后用EmulsionMask以及我之前提到的17-18步做MetalMask!瞬间有种Recursion的感觉有木有!!!

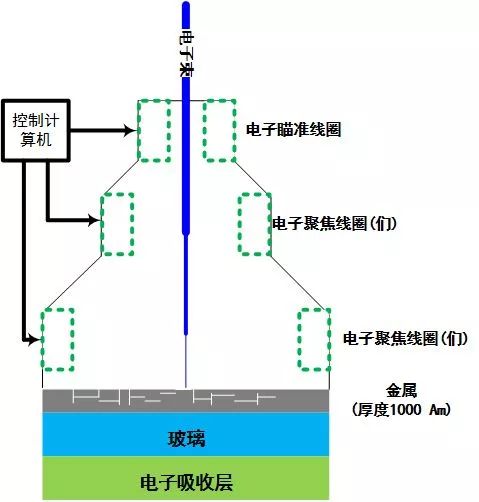

2.Electronbeam:

大概长这样

制作的时候移动的是底下那层. 电子束不移动.就像打印机一样把底下打一遍.

好处是精度特别高, 目前大多数高精度的(<100nm技术)都用这个掩膜. 坏处是太慢...

做好掩膜后:Feature Size = k*lamda / NA

k一般是0.4, 跟制作过程有关; lamda是所用光的波长; NA是从芯片看上去, 放大镜的倍率.

以目前的技术水平, 这个公式已经变了, 因为随着Feature Size减小, 透镜的厚度也是一个问题了

Feature Size = k * lamda / NA^2

恩.. 所以其实掩膜可以做的比芯片大一些. 至于具体制作方法, 一般是用高精度计算机探针 + 激光直接刻板. Photomask(掩膜) 的材料选择一般也比硅晶片更加灵活, 可以采用很容易被激光汽化的材料进行制作.

今天突然发现我还忘了一个很重要的点!找了一圈知乎找到了!多谢

@又见山人

!!

浸没式光刻

这个光刻的方法绝壁是个黑科技一般的点!直接把Lamda缩小了一个量级,Withnoextracost!你们说吼不吼啊!

FoodforThought:Wikipedia上面关于掩膜的版面给出了这样一幅图,假设用这样的掩膜最后做出来会是什么形状呢?

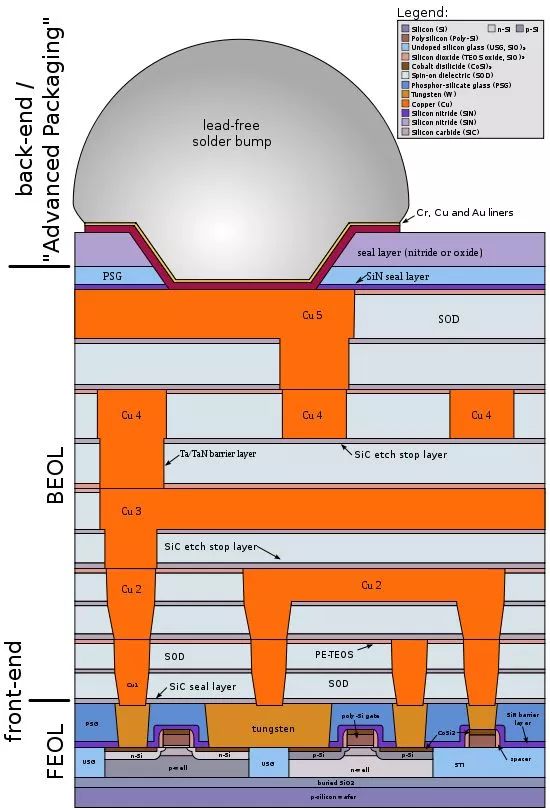

最终成型大概长这样:

其中, 步骤1-15 属于 前端处理 (FEOL), 也即如何做出场效应管

步骤16-18(加上许许多多的重复)属于后端处理(BEOL),后端处理主要是用来布线.最开始那个大芯片里面能看到的基本都是布线!一般一个高度集中的芯片上几乎看不见底层的硅片,都会被布线遮挡住.

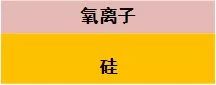

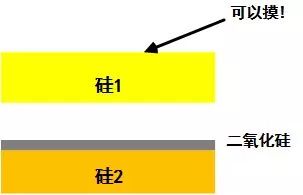

SOI(Silicon-on-Insulator)技术:

传统CMOS技术的缺陷在于:衬底的厚度会影响片上的寄生电容,间接导致芯片的性能下降.SOI技术主要是将源极/漏极和硅片衬底分开,以达到(部分)消除寄生电容的目的.

传统:

SOI:

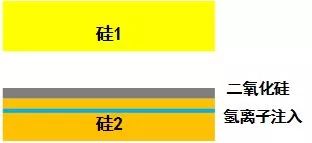

制作方法主要有以下几种(主要在于制作硅-二氧化硅-硅的结构, 之后的步骤跟传统工艺基本一致.)

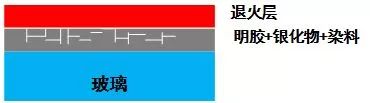

1.高温氧化退火:

在硅表面离子注入一层氧离子层

等氧离子渗入硅层, 形成富氧层

高温退火

成型.

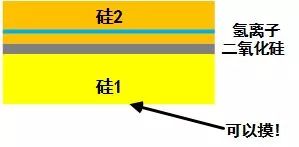

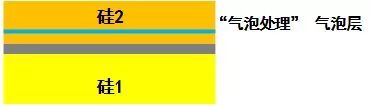

或者是2.WaferBonding(用两块!)

不是要做夹心饼干一样的结构吗?爷不差钱!来两块!

来两块!

对硅2进行表面氧化

对硅2进行氢离子注入

翻面

将氢离子层处理成气泡层

切割掉多余部分

成型!+再利用

光刻

离子注入

微观图长这样:

再次光刻+蚀刻

撤去保护, 中间那个就是Fin

门部位的多晶硅/高K介质生长

门部位的氧化层生长

长成这样

源极 漏极制作(光刻+ 离子注入)

初层金属/多晶硅贴片

蚀刻+成型

物理气相积淀长出表面金属层(因为是三维结构, 所有连线要在上部连出)

机械打磨(对!不打磨会导致金属层厚度不一致)

成型!

连线

处理器的制造过程可以大致分为沙子原料(石英)、硅锭、晶圆、光刻(平版印刷)、蚀刻、离子注入、金属沉积、金属层、互连、晶圆测试与切割、核心封装、等级测试、包装上市等诸多步骤,而且每一步里边又包含更多细致的过程。

下边就图文结合,一步一步看看:

沙子:硅是地壳内第二丰富的元素,而脱氧后的沙子(尤其是石英)最多包含25%的硅元素,以二氧化硅(SiO2)的形式存在,这也是半导体制造产业的基础。

硅熔炼:12英寸/300毫米晶圆级,下同。通过多步净化得到可用于半导体制造质量的硅,学名电子级硅(EGS),平均每一百万个硅原子中最多只有一个杂质原子。此图展示了是如何通过硅净化熔炼得到大晶体的,最后得到的就是硅锭(Ingot)。

单晶硅锭:整体基本呈圆柱形,重约100千克,硅纯度99.9999%。

第一阶段的合影。

硅锭切割:横向切割成圆形的单个硅片,也就是我们常说的晶圆(Wafer)。顺便说,这下知道为什么晶圆都是圆形的了吧?

晶圆:切割出的晶圆经过抛光后变得几乎完美无瑕,表面甚至可以当镜子。事实上,Intel自己并不生产这种晶圆,而是从第三方半导体企业那里直接购买成品,然后利用自己的生产线进一步加工,比如现在主流的45nm HKMG(高K金属栅极)。值得一提的是,Intel公司创立之初使用的晶圆尺寸只有2英寸/50毫米。

第二阶段合影。

光刻胶(Photo Resist):图中蓝色部分就是在晶圆旋转过程中浇上去的光刻胶液体,类似制作传统胶片的那种。晶圆旋转可以让光刻胶铺的非常薄、非常平。

光刻:光刻胶层随后透过掩模(Mask)被曝光在紫外线(UV)之下,变得可溶,期间发生的化学反应类似按下机械相机快门那一刻胶片的变化。掩模上印着预先设计好的电路图案,紫外线透过它照在光刻胶层上,就会形成微处理器的每一层电路图案。一般来说,在晶圆上得到的电路图案是掩模上图案的四分之一。

光刻:由此进入50-200纳米尺寸的晶体管级别。一块晶圆上可以切割出数百个处理器,不过从这里开始把视野缩小到其中一个上,展示如何制作晶体管等部件。晶体管相当于开关,控制着电流的方向。现在的晶体管已经如此之小,一个针头上就能放下大约3000万个。

第三阶段合影。

溶解光刻胶:光刻过程中曝光在紫外线下的光刻胶被溶解掉,清除后留下的图案和掩模上的一致。

蚀刻:使用化学物质溶解掉暴露出来的晶圆部分,而剩下的光刻胶保护着不应该蚀刻的部分。

清除光刻胶:蚀刻完成后,光刻胶的使命宣告完成,全部清除后就可以看到设计好的电路图案。

第四阶段合影。

光刻胶:再次浇上光刻胶(蓝色部分),然后光刻,并洗掉曝光的部分,剩下的光刻胶还是用来保护不会离子注入的那部分材料。

离子注入(Ion Implantation):在真空系统中,用经过加速的、要掺杂的原子的离子照射(注入)固体材料,从而在被注入的区域形成特殊的注入层,并改变这些区域的硅的导电性。经过电场加速后,注入的离子流的速度可以超过30万千米每小时。

清除光刻胶:离子注入完成后,光刻胶也被清除,而注入区域(绿色部分)也已掺杂,注入了不同的原子。注意这时候的绿色和之前已经有所不同。

第五阶段合影。

晶体管就绪:至此,晶体管已经基本完成。在绝缘材(品红色)上蚀刻出三个孔洞,并填充铜,以便和其它晶体管互连。

电镀:在晶圆上电镀一层硫酸铜,将铜离子沉淀到晶体管上。铜离子会从正极(阳极)走向负极(阴极)。

铜层:电镀完成后,铜离子沉积在晶圆表面,形成一个薄薄的铜层。

第六阶段合影。

抛光:将多余的铜抛光掉,也就是磨光晶圆表面。

金属层:晶体管级别,六个晶体管的组合,大约500纳米。在不同晶体管之间形成复合互连金属层,具体布局取决于相应处理器所需要的不同功能性。芯片表面看起来异常平滑,但事实上可能包含20多层复杂的电路,放大之后可以看到极其复杂的电路网络,形如未来派的多层高速公路系统。

第七阶段合影。

晶圆测试:内核级别,大约10毫米/0.5英寸。图中是晶圆的局部,正在接受第一次功能性测试,使用参考电路图案和每一块芯片进行对比。

晶圆切片(Slicing):晶圆级别,300毫米/12英寸。将晶圆切割成块,每一块就是一个处理器的内核(Die)。

丢弃瑕疵内核:晶圆级别。测试过程中发现的有瑕疵的内核被抛弃,留下完好的准备进入下一步。

第八阶段合影。

单个内核:内核级别。从晶圆上切割下来的单个内核,这里展示的是Core i7的核心。

封装:封装级别,20毫米/1英寸。衬底(基片)、内核、散热片堆叠在一起,就形成了我们看到的处理器的样子。衬底(绿色)相当于一个底座,并为处理器内核提供电气与机械界面,便于与PC系统的其它部分交互。散热片(银色)就是负责内核散热的了。

处理器:至此就得到完整的处理器了(这里是一颗Core i7)。这种在世界上最干净的房间里制造出来的最复杂的产品实际上是经过数百个步骤得来的,这里只是展示了其中的一些关键步骤。

第九阶段合影。

等级测试:最后一次测试,可以鉴别出每一颗处理器的关键特性,比如最高频率、功耗、发热量等,并决定处理器的等级,比如适合做成最高端的Core i7-975 Extreme,还是低端型号Core i7-920。

装箱:根据等级测试结果将同样级别的处理器放在一起装运。

零售包装:制造、测试完毕的处理器要么批量交付给OEM厂商,要么放在包装盒里进入零售市场。

-

芯片

+关注

关注

457文章

51344浏览量

428172 -

晶圆

+关注

关注

52文章

4999浏览量

128411 -

晶体管

+关注

关注

77文章

9796浏览量

139053

原文标题:【科普】芯片里面有几千万的晶体管是怎么实现的?

文章出处:【微信号:TechSugar,微信公众号:TechSugar】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

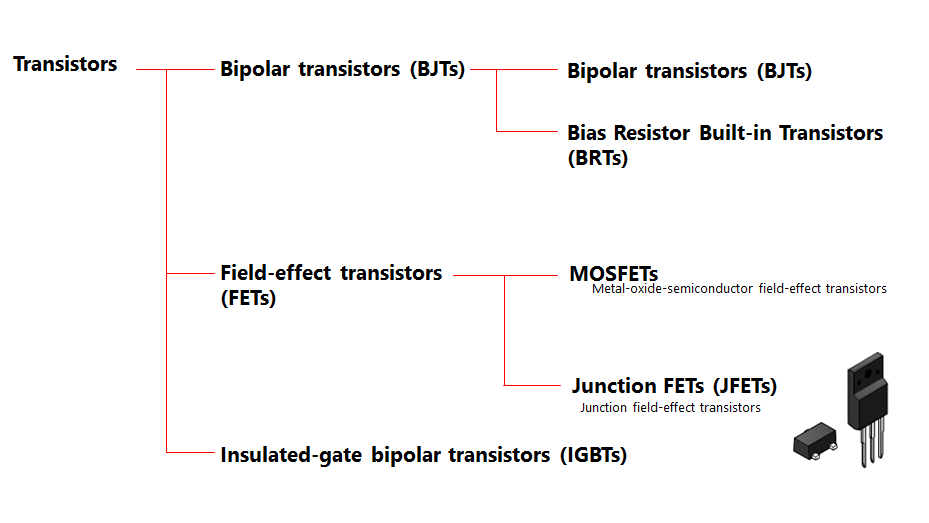

晶体管故障诊断与维修技巧 晶体管在数字电路中的作用

晶体管与场效应管的区别 晶体管的封装类型及其特点

晶体管的基本工作模式

NMOS晶体管和PMOS晶体管的区别

CMOS晶体管和MOSFET晶体管的区别

什么是单极型晶体管?它有哪些优势?

芯片晶体管的深度和宽度有关系吗

芯片中的晶体管是怎么工作的

晶体管电流的关系有哪些类型 晶体管的类型

PNP晶体管符号和结构 晶体管测试仪电路图

晶体管功率继电器的基本介绍

苹果M3芯片的晶体管数量

M3芯片有多少晶体管

什么是达林顿晶体管?达林顿晶体管的基本电路

芯片里面有几千万的晶体管是怎么实现的

芯片里面有几千万的晶体管是怎么实现的

评论