声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

原理图

+关注

关注

1304文章

6364浏览量

235535 -

网络

+关注

关注

14文章

7604浏览量

89365 -

PADS

+关注

关注

80文章

808浏览量

107995

发布评论请先 登录

相关推荐

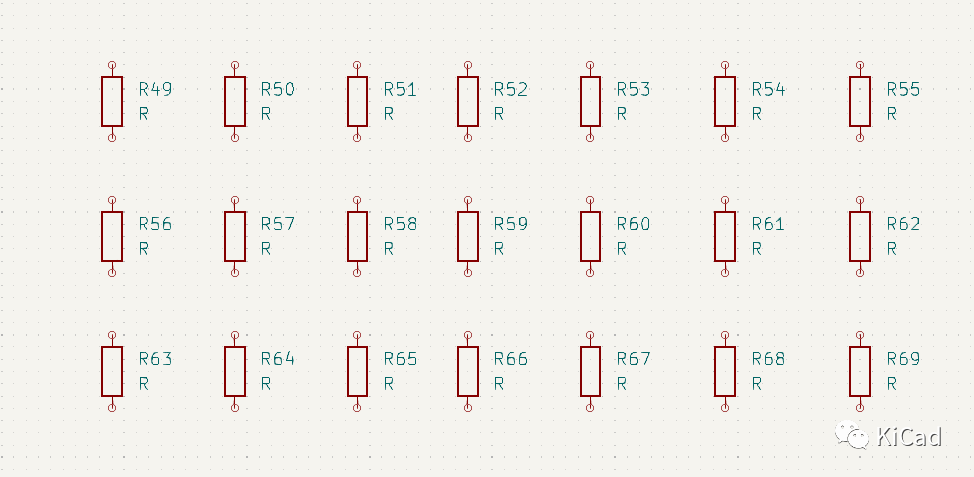

如何在KiCad原理图中连续摆放同一个器件符号?

“ KiCad 将原理图符号摆放到图纸上的默认操作设置与其它 EDA 工具略有不同。因此有些小伙伴会抱怨 KiCad 操作不够方便,这其实是个误解,KiCad 完全可以实现相同的功能。”

如何在Linux系统上设置站群服务器IP地址

在Linux系统上设置站群服务器的IP地址,可以通过以下步骤进行,主机推荐小编为您整理发布如何在Linux系统上设置站群服务器IP地址。

时序约束一主时钟与生成时钟

的输出,对于Ultrascale和Ultrascale+系列的器件,定时器会自动地接入到GT的输出。 1.2 约束设置格式 主时钟约束使用命令create_clock进行创建,进入Timing

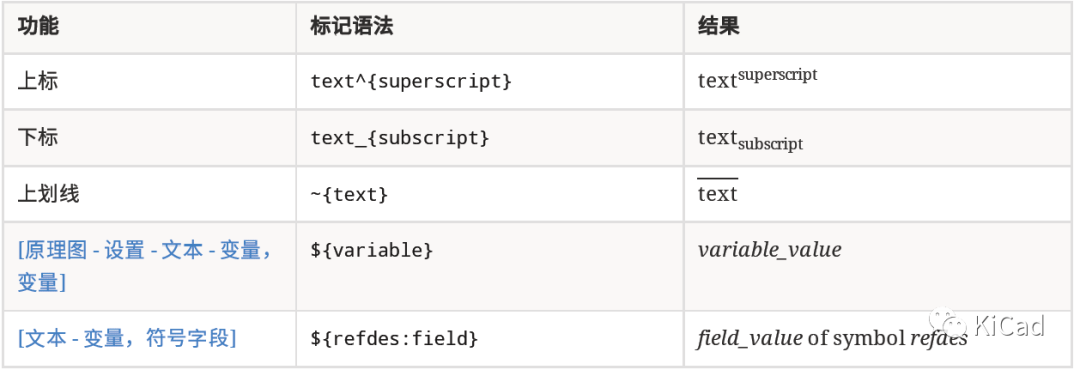

如何在文本字段中使用上标、下标及变量

在KiCad的任何文本字段中,都可以通过以下的方式实现上标、下标、上划线以及显示变量及字段值的描述: 文本变量“文本变量”可以在 原理图设置->工程->文本变量 中设置。下图中

如何在应用中正确设置THVD1505和SN65HVD888

电子发烧友网站提供《如何在应用中正确设置THVD1505和SN65HVD888.pdf》资料免费下载

发表于 09-18 10:25

•0次下载

原理图中的vcc在pcb中如何处理

在电子设计和制造过程中,原理图(schematic diagram)和印刷电路板(PCB)设计是两个关键步骤。原理图中的VCC通常代表电源电压,它是电路中所有组件的电源来源。在将原理图转换

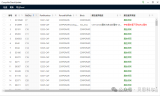

如何快速检测原理图中的元器件与PLM系统的一致性,提高原理图设计准确性

背景介绍保证原理图中的元器件来源于公司的PLM系统、ERP系统的,是输出有效BOM的根源,初始BOM的准确率,能大大降低ECN的数量,提高生产备料的时效,缩短采购周期。然而,原理图设计过程中,由于

如何快速检测原理图中的元器件与PLM系统的一致性?

保证原理图中的元器件来源于公司的PLM系统、ERP系统的,是输出有效BOM的根源,初始BOM的准确率,能大大降低ECN的数量,提高生产备料的时效,缩短采购周期。

Xilinx FPGA的约束设置基础

LOC约束是FPGA设计中最基本的布局约束和综合约束,能够定义基本设计单元在FPGA芯片中的位置,可实现绝对定位、范围定位以及区域定位。

发表于 04-26 17:05

•1393次阅读

如何在原理图中设置特殊约束

如何在原理图中设置特殊约束

评论