在一个环境中实施从合成到塑封式布局和布线以及比特流生成的全套 FPGA 设计。界面中内置了用于运行布局和布线的常用选项,并在与合成结果相同的位置提供所有报告。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1637文章

21841浏览量

608516 -

设计

+关注

关注

4文章

819浏览量

70043

发布评论请先 登录

相关推荐

一文讲清芯片封装中的塑封材料:环氧塑封料(EMC)成分与作用

在半导体封装领域,塑封技术以其低成本、高效率、良好的保护性能,成为封装工艺中的关键一环。Mold工艺,作为塑封技术的重要组成部分,通过特定的模具将芯片等组件包裹在加热的模塑材料中,固化后形成坚硬

Vivado之实现布局布线流程介绍

一、前言 本文将介绍Vivado进行综合,以及布局布线的内部流程,熟悉该流程后结合Settings中对应的配置选项,对于时序收敛调试将更具有针对性。 二、Implementation(实现) 实现

塑封、切筋打弯及封装散热工艺设计

本文介绍塑封及切筋打弯工艺设计重点,除此之外,封装散热设计是确保功率器件稳定运行和延长使用寿命的重要环节。通过优化散热通道、选择合适的材料和结构以及精确测量热阻等步骤,可以设计出具有优异散热

塑封器件绝缘失效分析

塑封器件绝缘失效机理探究与改进策略塑封器件因其紧凑、轻便、经济及卓越的电学特性,在电子元件封装行业中占据着重要地位。但随着其在更严苛环境下的应用需求增加,传统工业级塑封材料和技术的局限性逐渐显现。金

高速ADC PCB布局布线技巧分享

在高速模拟信号链设计中,印刷电路板(PCB)布局布线需 要考虑许多选项,有些选项比其它选项更重要,有些选项 则取决于应用。最终的答案各不相同,但在所有情况下, 设计工程师都应尽量消除最佳做法

FPGA的高速接口应用注意事项

、LVDS高速接口等,FPGA需要实现相应的关键技术以支持数据传输。

布线与布局 :

时钟信号布线:FPGA和高速DAC的时钟信号必须保证

发表于 05-27 16:02

FPGA布局布线优化策略(五)

对设计者很通常的情况是花费几天或几周的时间围绕一个设计来满足时序,甚至多半利用上面描述的自动种子变化,只面对可以起伏通过已有布局的小改变和时序特性完全改变。

发表于 04-01 12:35

•929次阅读

FPGA布局布线优化技术

寄存器排序是布局工具把多位寄存器的相邻位分组放进单个逻辑元件所利用的方法。大多数基于单元的逻辑元件有不止一个触发器,因此,相邻位放置在一起,时序可以被优化。

发表于 03-29 11:30

•485次阅读

FPGA布局布线的可行性 FPGA布局布线失败怎么办

随着电子技术的进步.FPGA逻辑电路能完成的功能越来越多,同样也带来了一个很大的问题,即逻辑电路的规模越来越大,这意味着RTL代码到FPGA的映射、布局布线所花费的时间也越来越长。

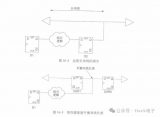

FPGA设计的塑封式布局和布线介绍

FPGA设计的塑封式布局和布线介绍

评论