本视频将会概述基本的约束管理概念,并演示如何为密集的高约束 PCB 设计创建和管理约束。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

pcb

+关注

关注

4418文章

23979浏览量

426395 -

设计

+关注

关注

4文章

829浏览量

71497

发布评论请先 登录

相关推荐

热点推荐

电压放大器在主动约束层阻尼板研究测试中的应用

主动约束层阻尼结构采用压电或其他智能材料取代经典约束层阻尼结构中的约束层,并通过引入主动控制系统,进一步增强约束阻尼层对振动能量的耗散能力。即使在主动控制系统关闭或失效的情况下,仍能保

Vivado时序约束中invert参数的作用和应用场景

在Vivado的时序约束中,-invert是用于控制信号极性的特殊参数,应用于时钟约束(Clock Constraints)和延迟约束(Delay Constraints)中,用于指定信号的有效边沿或逻辑极性。

输入引脚时钟约束_Xilinx FPGA编程技巧-常用时序约束详解

基本的约束方法

为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取。最普遍的三种路径以及异常路径为:

输入路径(Input Path),使用输入约束

寄存器到寄存器路径

发表于 01-16 08:19

时序约束问题的解决办法

Time 是否满足约束。

我们要留意的是 WNS 和 WHS 两个数值,如果这两个数值为红色,就说明时序不满足约束。下面将解释怎么解决这个问题。

1. Setup Time 违例

Setup

发表于 10-24 09:55

关于综合保持时间约束不满足的问题

1、将 nuclei-config.xdc 和 nuclei-master.xdc 加入到项目工程中,综合得到时序约束报告如下:

保持时间约束不满足,分析原因,发现所有不满足均出现在

发表于 10-24 07:42

技术资讯 I Allegro 设计中的走线约束设计

本文要点在进行时序等长布线操作的时候,在布线操作的时候不管你是走蛇形线还是走折线,约束管理器会自动帮你计算长度、标偏差,通过精确控制走线长度,来实现信号的时序匹配。约束设计就是一套精准的导航系统

技术资讯 I 图文详解约束管理器-差分对规则约束

本文要点你是否经常在Layout设计中抓瞎,拿着板子无从下手,拿着鼠标深夜狂按;DDR等长没做好导致系统不稳定,PCIe没设相位容差造成链路训练失败……这些都是血泪教训,关键时刻需要靠约束管理器救命

高速PCB设计挑战 Allegro Skill布线功能 自动创建match_group

在进行高速PCB设计的过程中,常常会遇到一个挑战,那就是高速信号的时序匹配问题。为了确保信号的同步到达,设计者需要对特定的高速信号组进行等长设计。手动进行这样的操作可能会非常繁琐且容易出错。凡亿

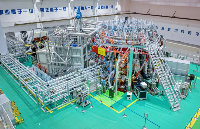

再创新高,“中国环流三号”实现百万安培亿度高约束模

近日,由核工业西南物理研究院(简称“西物院”)研制的新一代人造太阳“中国环流三号”再次创下我国聚变装置运行新纪录——实现百万安培亿度高约束模(H模),即装置同时实现等离子体电流100万安培、离子温度

PCB设计,轻松归档,效率倍增!

PCB设计一键归档简化流程,提升效率,一键归档,尽在掌握!在电子产品设计领域,PCB设计工作完成后,需要输出不同种类的文件给到PCB生产商,产线制造部门,测试部门,同时还需将设计文件进行归档管

西门子再收购EDA公司 西门子宣布收购Excellicon公司 时序约束工具开发商

精彩看点 此次收购将帮助系统级芯片 (SoC) 设计人员通过经市场检验的时序约束管理能力来加速设计,并提高功能约束和结构约束的正确性 西门子宣布 收购 Excellicon 公司

PanDao:实际约束条件下成像系统的初始结构的生成

,受限于手机内部严苛的长度约束,使用高非球面化透镜就成为了必然选择。下文将展示几个FTR技术应用的案例,并将生成的光学设计结果与生产信息进行权重整合。为此,采用最新研发的PanDao软件 [3-5

发表于 05-07 08:57

如何为密集的高约束PCB设计创建和管理约束

如何为密集的高约束PCB设计创建和管理约束

评论