在遵循管脚特定的规则和约束的同时,可以在 PCB 上的多个 FPGA 之间自动优化信号管脚分配。减少布线层数,最大限度地减少 PCB 上的交叉数量并缩短总体走线长度,以及减少信号完整性问题,从而提高完成率并缩短 FPGA 的布线时间。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22516浏览量

639694 -

pcb

+关注

关注

4418文章

23982浏览量

426509

发布评论请先 登录

相关推荐

热点推荐

S32K3的ADC启动时间需要大约30ms左右,这是正常的吗?如何缩短这个时间?

我在使用S32K3的ADC,测试发现从上电初始化ADC,执行校准,开启转换,到首次完成采集,需要大约30ms左右,这是正常的吗?如何缩短这个时间?

发表于 04-24 06:28

人工智能数据中心的光纤布线策略

随着人工智能(AI)技术的飞速发展,数据中心的光纤布线策略正面临前所未有的挑战和机遇。AI的高带宽需求、低延迟要求以及大规模并行计算的特点,对数据中心的光纤布线提出了更高的要求。本文将从多个方面探讨

高频PCB布线“避坑指南”:4大核心技巧让信号完整性提升90%

技巧 一、核心布线原则 多层板设计 高频电路集成度高,采用至少四层板(顶层、底层、电源层、地层),利用中间层设置屏蔽和就近接地,降低寄生电感,缩短信号传输路径,减少交叉干扰。例如,四层板比双面板噪声低20dB。 电源层与地平面相邻,利用平面电容

Altera发布 Quartus® Prime 专业版和 FPGA AI 套件 25.3 版:编译更快,智能更强

投产以来编译时间缩短多达 27%,同时显著提升了 AI 工具的易用性; 得益于增强型编译器和架构优化,设计人员平均可节省

如何缩短电能质量在线监测装置的抗干扰能力验证时间?

缩短电能质量在线监测装置的抗干扰能力验证时间,核心是 “ 聚焦关键干扰、优化测试流程、复用技术工具 ”,在保障核心验证指标(精度稳定性、事件捕捉完整性)不打折的前提下,砍掉冗余步骤、提升并行效率

低压布线与传统布线:有什么区别?

低压布线与传统布线在电压范围、应用场景、设计要求、安全规范及材料选择等方面存在显著差异。以下是具体对比分析: 1. 电压范围与定义 低压布线: 电压等级:通常指交流电压在1000V以下或直流电

亚马逊:调用订单退款API自动化处理售后请求,缩短用户等待时间

在电商运营中,售后处理效率直接影响用户体验和平台声誉。亚马逊作为全球领先的电商平台,其订单退款API为卖家提供了强大的自动化工具,帮助高效处理退款请求,显著缩短用户等待时间。本文将逐步介绍

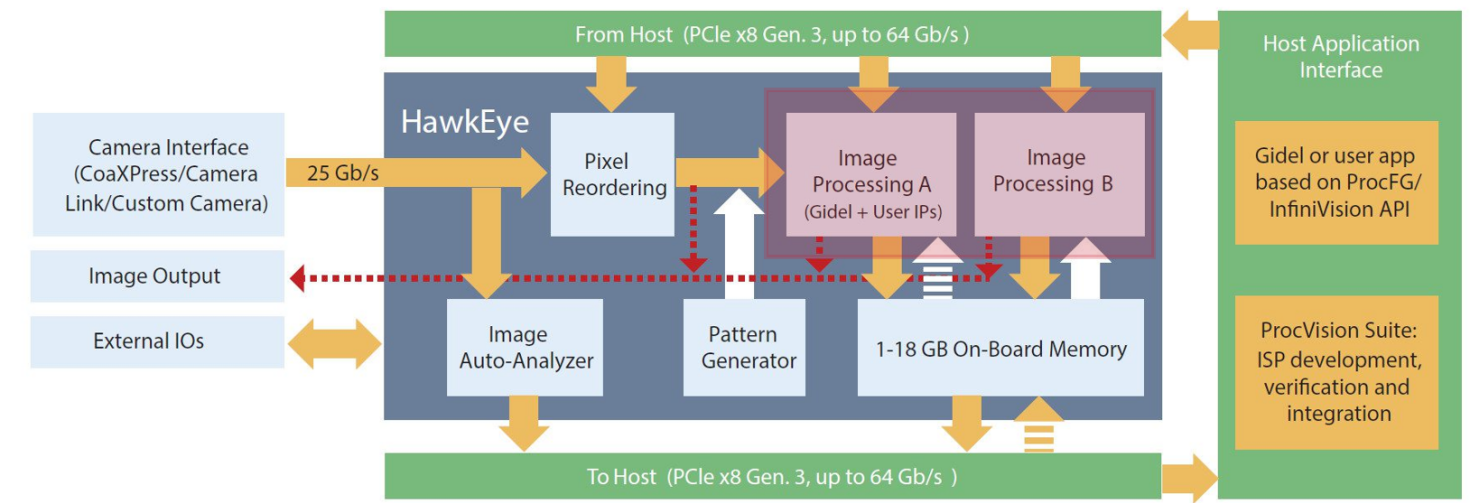

FPGA 加持,友思特图像采集卡高速预处理助力视觉系统运行提速增效

图像预处理是图像处理关键环节,可优化数据传输、减轻主机负担,其算法可在FPGA等硬件上执行。友思特FPGA图像采集卡凭借FPGA特性,能缩短处理时间

从发明到 AI 加速:庆祝 FPGA 创新 40 周年

设计芯片时,如果规格或需求在中途、甚至在制造完成后发生变化,他们可以重新定义芯片功能以执行不同的任务。这种灵活性令新芯片设计的开发速度更快,从而缩短了新产品的上市时间,并提供了 ASIC 的替代方案。 FPGA 对市场的影响

发表于 06-05 17:32

•1467次阅读

高层数层叠结构PCB的布线策略

高层数 PCB 的布线策略丰富多样,具体取决于 PCB 的功能。这类电路板可能涉及多种不同类型的信号,从低速数字接口到具有不同信号完整性要求的多个高速数字接口。从布线规划和为各接口分配信号层的角度来看,这无疑是一项极具挑战性的任

如何缩短多个FPGA的布线时间

如何缩短多个FPGA的布线时间

评论