虽然索尼PS5主机在今年甚至明年上半年都见不到,但官方已经等不及地进行连珠炮式预热。

在2019年6月刊的Official PlayStation杂志中,一份来自索尼的官方说明称“一块超高速的SSD对我们的下一代主机非常关键。我们希望让屏幕加载时间成为过去式,从而让开发者们打造更无缝的游戏体验。”

其实,在前不久索尼PS首席架构师Mark Cerny的采访中,他就向记者演示了新主机硬盘读写的巨大优势,同样是载入《漫威蜘蛛侠》游戏,PS4 Pro需要15秒,而“PS5”原型机只要0.5秒。

由于PS5确定基于AMD Zen 2架构处理器打造,我们有理由猜测这块SSD可能支持的是PCIe 4.0带宽接口,从而进一步突破I/O瓶颈。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

索尼

+关注

关注

18文章

3188浏览量

104832 -

SSD

+关注

关注

21文章

2859浏览量

117374 -

PCIe

+关注

关注

15文章

1235浏览量

82596 -

游戏机

+关注

关注

9文章

299浏览量

33435

发布评论请先 登录

相关推荐

PCIe 4.0与3.0的区别 PCIe设备的故障排除方法

PCIe 4.0与3.0的区别 PCIe(Peripheral Component Interconnect Express)是一种高速计算

PCIe 4.0与PCIe 3.0的性能对比

随着科技的快速发展,计算机硬件也在不断地更新换代。PCI Express(PCIe)作为一种高速串行计算机扩展总线标准,广泛应用于计算机硬件连接,如显卡、固态硬盘等。 1. 带宽对比

今日看点丨消息称下一代奥迪 A5将首次搭载华为智驾方案;思科全球裁员6300人

1. 消息称下一代奥迪 A5 在中国将首次搭载华为智驾方案 据报道,下一代奥迪 A5 基于 PPC 平台打造,在中国将

发表于 08-15 11:31

•1089次阅读

FPGA的PCIE接口应用需要注意哪些问题

和带宽。

时钟速度和同步 :

FPGA的时钟管理是实现高性能PCIe设计的关键。如果时钟频率设置不当或时钟源不稳定,可能会导致数据丢失和性能下降。

信号完整性 :

高速信号在FPG

发表于 05-27 16:17

高性能NVMe主机控制器,Xilinx FPGA PCIe 3

NVMe队列优先级仲裁(循环仲裁或加权循环仲裁)机制,实现多个DMA通道对同一块PCIe SSD的高效访问,从而达到多路数据通道访问的并行需求和QoS要求。1.1特性Ø

发表于 04-20 14:41

Xilinx FPGA高性能NVMe SSD主机控制器,NVMe Host Controller IP

循环仲裁)机制,实现多个DMA通道对同一块PCIe SSD的高效访问,从而达到多路数据通道访问的并行需求和QoS要求。1.1特性Ø支持Ultrascale+,Ultrascale,7

发表于 03-27 17:23

Xilinx FPGA NVMe主机控制器IP,高性能版本介绍应用

,使用NVMe的多队列特性,NVMe Host Controller IP支持灵活配置DMA读写的通道个数,按照NVMe队列优先级仲裁机制,实现多个DMA通道对同一块PCIe SSD的

发表于 03-09 13:56

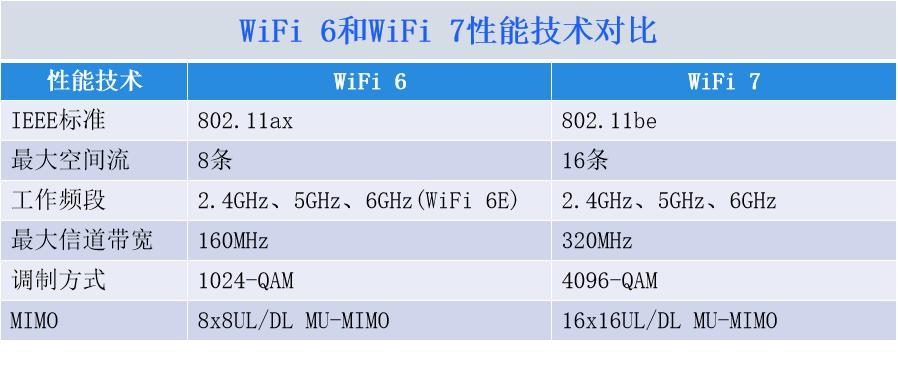

新一代工业级WiFi 7无线网卡,赋能工业4.0

继WiFi 6E之后,LR-LINK联瑞全新一代PCIe4.0 x1 WiFi 7和BT5.4二合一无线网卡(产品型号:LRIWF-BE200)于2月正式发布,从高速率、低延迟、抗干扰

Xilinx FPGA NVMe Host Controller IP,NVMe主机控制器

SSD,使用NVMe的多队列特性,NVMe Host Controller IP支持灵活配置DMA读写的通道个数,按照NVMe队列优先级仲裁机制,实现多个DMA通道对同一块PCIe

发表于 02-21 10:16

索尼下一代新主机将搭载一块超高速SSD 或支持PCIe4.0带宽接口

索尼下一代新主机将搭载一块超高速SSD 或支持PCIe4.0带宽接口

评论