有些朋友不理解为什么STM32时钟要先倍频N倍,再分频?你会担心这个值太大吗?

1写在前面

STM32时钟的功能,可以说是越来越强大了。

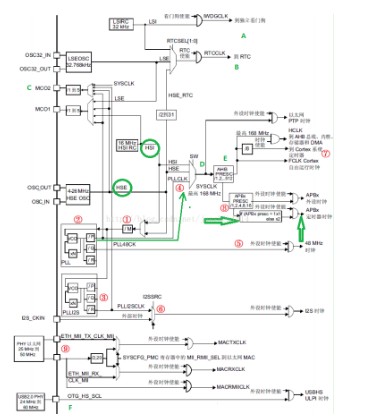

从各个系列的时钟树可以看得出来,最早F1系列的时钟功能相对比较简单,到这后面H7、G0的时钟越来越丰富。

今天讲述一下其中的PLL环节。

2关于PLL

什么是PLL?

PLL:Phase Locked Loop锁相环。

PLL用于振荡器中的反馈技术,通常需要外部的输入信号与内部的振荡信号同步。

一般的晶振由于工艺与成本原因,做不到很高的频率,而在需要高频应用时,由相应的器件VCO,实现转成高频,但并不稳定,故利用锁相环路就可以实现稳定且高频的时钟信号。

每一块STM32处理器至少都有一个PLL,有的甚至有好几个PLL。

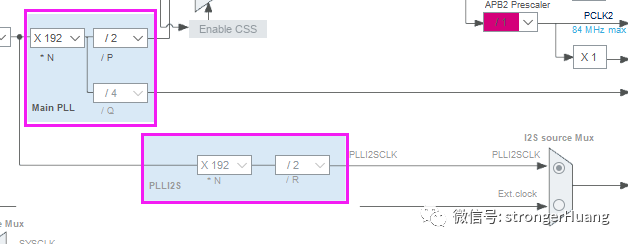

比如,F4有两个PLL:

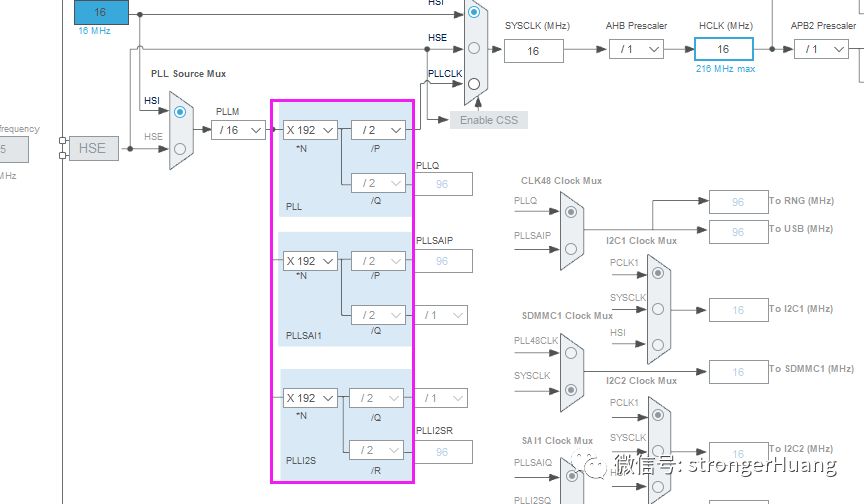

F7有三个PLL:

当然,每个MCU型号不同,其PLL数量,及功能也有差异,具体需要看相应手册。

3STM32CubeMX配置时钟树

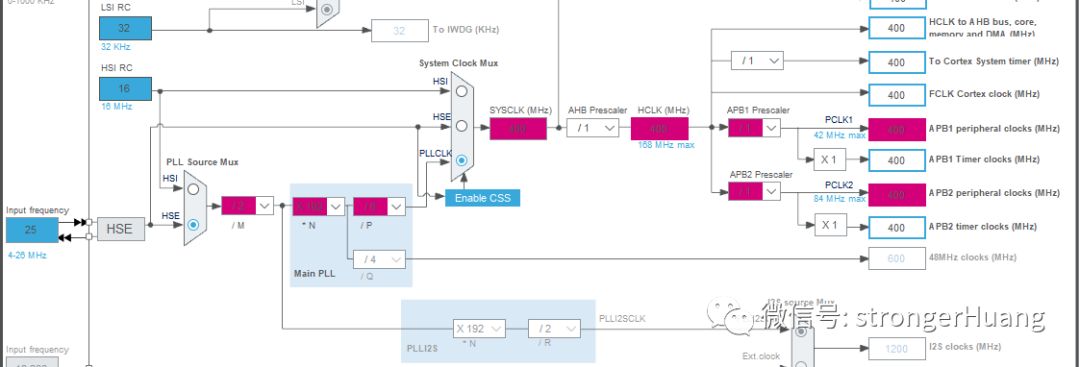

STM32CubeMX配置时钟不用担心出错。

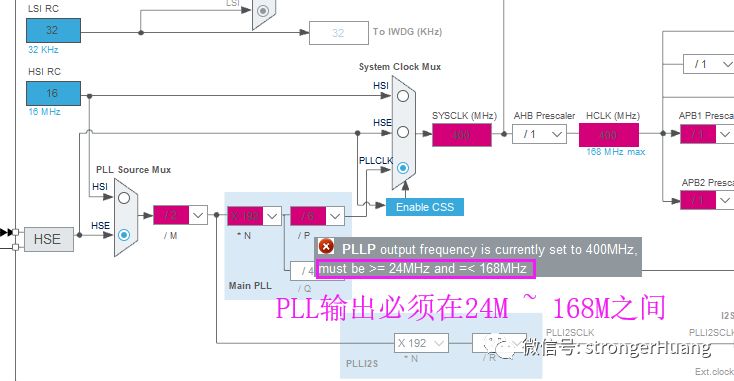

原因很简单,这个工具配置时钟树,如果出错,会有红色警告。

如下图:

具体每一个红色警告错误的原因,将光标移到红色警告过会有相应提示信息。

比如,输出PLLP值超过规定范围:

有这个提示信息,再也不怕配置出错了。

PLL的倍频和分频值

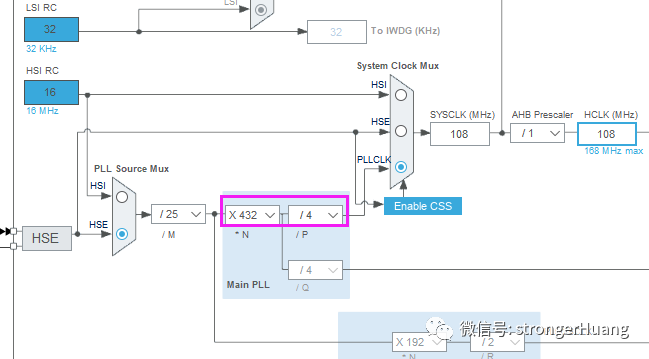

有人觉得前面倍频N值很大(如下图),这样会不会出问题?

答案肯定是不会。但不建议将参数N设置为最大值。

特定时钟频率

有些时候,我们要求有特定时钟频率,比如USB,ETH等。这个时候PLL参数就需要合理才行。

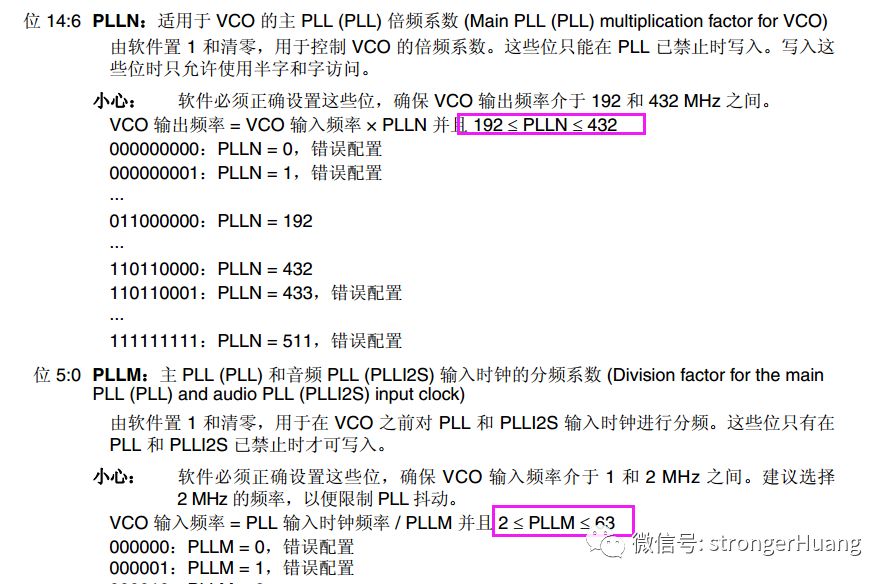

4STM32手册可查看PLL参数范围

STM32的时钟,在之前使用标准库,或者寄存器时,使用的晶振频率不是官方推荐的,很多人就会搞晕。

那么,就只有参看对应手册,手册上是有明确说明的。比如F4手册RCC章节,详细说明的PLL各参数值范围。

-

STM32

+关注

关注

2270文章

10901浏览量

356174 -

分频

+关注

关注

0文章

241浏览量

24864

原文标题:为什么STM32时钟要先倍频N倍,再分频?

文章出处:【微信号:mcuworld,微信公众号:嵌入式资讯精选】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

STM32时钟要先倍频N倍再分频的原因是什么?

STM32时钟要先倍频N倍再分频的原因是什么?

评论