随着制程的进一步缩小,芯片制造的难度确实已经快接近理论极限了。

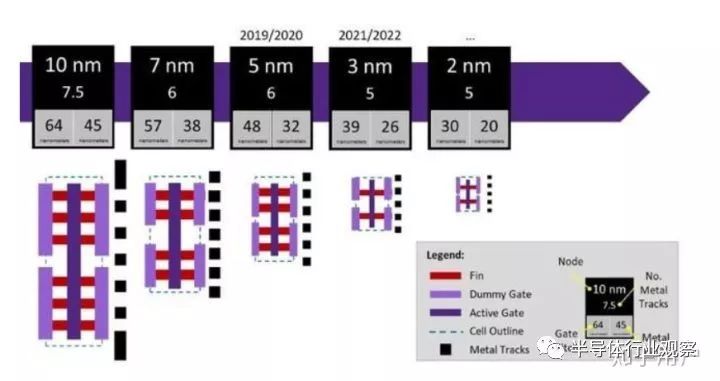

首先简单介绍一下当前芯片先进制程的发展现状,下图是近些年芯片制程的发展图,Intel 曾一度处于业内领头羊地位,引领半导体先进制程的发展,但是从14nm 到10nm 制程时遇到了很多麻烦,一度处于难产状态。Intel在10nm 量产后又迟迟难以进一步推进,目前7nm 量产还没有一个确定的日期, 虽然Intel 的10nm工艺有着比竞争对手更高的晶体管密度。

半导体制程发展

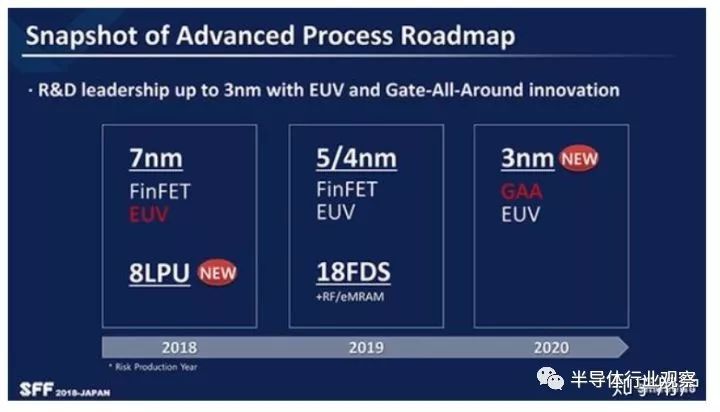

我们再来看看竞争对手,目前拥有最先进制程的厂商无疑非台积电 (tsmc)莫属,台积电在2018年最早实现了7nm 制程的突破并量产, 而5nm 制程工艺也已指日可待,预计在2020年实现量产。

台积电制程规划

紧随其后的是三星,在台积电之后也成功实现了7nm 制程的量产,所不同的是,三星提前使用了EUV光刻技术来进行7nm 工艺,而台积电则把EUV留到了5nm 以后的制程。但是,相对而言,三星的7nm 工艺不如台积电的7nm 工艺,台积电也因此在7nm 制程工艺上斩获了大量的订单。

三星制程规划

而曾今从AMD分离的半导体大厂格罗方德则干脆直接放弃了7nm工艺的研发,表示玩不起了。

另外就算有再强的研发实力和经济实力,也不表示这个游戏可以一直玩下去,详细内容可以参考以下话题,目前的制程工艺已经在逼近理论极限。

我们再回到这个问题本身上来,半导体制造的难度最主要是制程的实现,半导体厂商之间的竞争也体现在先进制程的突破上。以下将从制程和其他几个方面作简单介绍:

先进制程

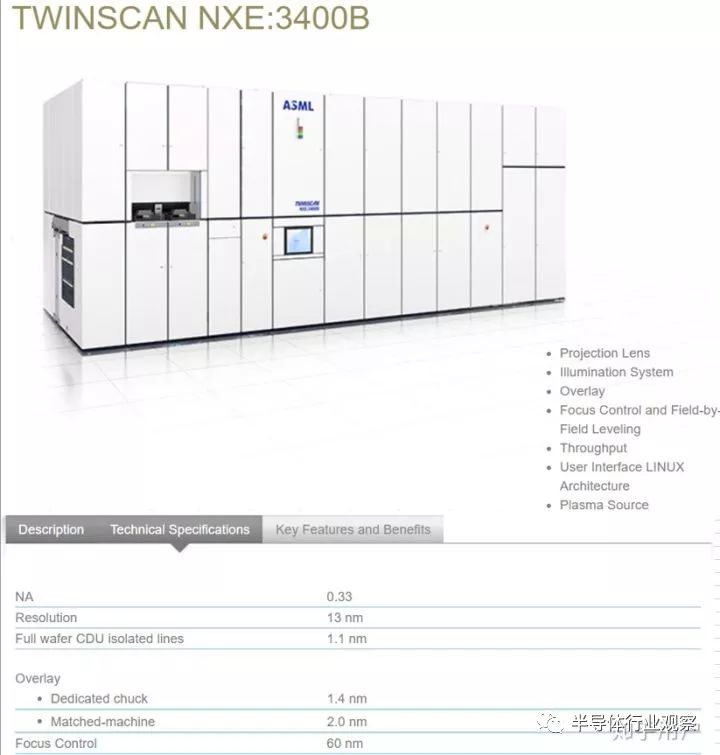

半导体工艺制程的实现需要很多的工艺相互配合,主要的有光刻工艺,蚀刻工艺,金属工艺,化学气相沉积工艺,离子注入工艺等。由于芯片的制造过程中所有的图形都是有光刻工艺决定的,而其他工艺只是在光刻工艺制作出的模板上进一步加工,因此直接决定制程的就是光刻工艺。光刻工艺的精度又是由***的光学分辨率决定:

ASML设备发展

顶尖***邻域荷兰ASML公司一家独大,每一次制程的进步和新型***的推出都是密不可分的。最新的7nm 制程工艺的量产就得益于 ASML EUV ***的成功研制,实际上由于大功率EUV光源实现困难,EUV***只到2018年才正式进入量产, 而不是上图计划中的2010年左右。

ASML EUV

***除了对分辨率的要求以外,对于对准(Overlay)有更高的要求,比如上图中最新的EUV ***对准的误差是1.4nm, 并且达到这一水平还需要在高速状态下实现,有一个说法是:

“相当于两架大飞机从起飞到降落,始终齐头并进。一架飞机上伸出一把刀,在另一架飞机的米粒上刻字,不能刻坏了。”

实际上这个说法并不夸张,只有在这种精度级别上才能实现目前所需的制程。

当然,光刻工艺精度的提高,对其他蚀刻等工艺也会提出更高的要求,只有所有的工艺都能够完美的配合时,才能实现新一代制程的导入。

工艺流程

半导体工艺类型只有我上面提到的不到10个(光刻,蚀刻,化学气相沉积等),但是实际上由于芯片的制备是一层一层的加工制造,并且制程越先进,晶体管密度越大,相应的所需要的层数也越多,因此需要各种类型的工艺反复的进行加工。芯片从晶圆开始加工到结束可能需要300道以上的工序,而任何一道工序稍有失误就可能导致大量的芯片报废。并且很多工艺都是没有挽救余地的,中间只要有一个工艺发生偏差就只能报废处理,还有很多时候很小的偏差只有等到芯片制造完成进行电性能测试的时候才能发现,这样造成的损失就更加庞大。

芯片剖面图

因此在整个工艺流程中,设备的状态,工艺参数,材料的供应,环境因素等等都可能导致严重的后果,例如台积电最近的两次事故,对于台积电这种具有丰富经验的先进制程半导体厂商都难以预防,那些新建立的芯片制造厂商可能交学费都要交到破产了。

生产运营

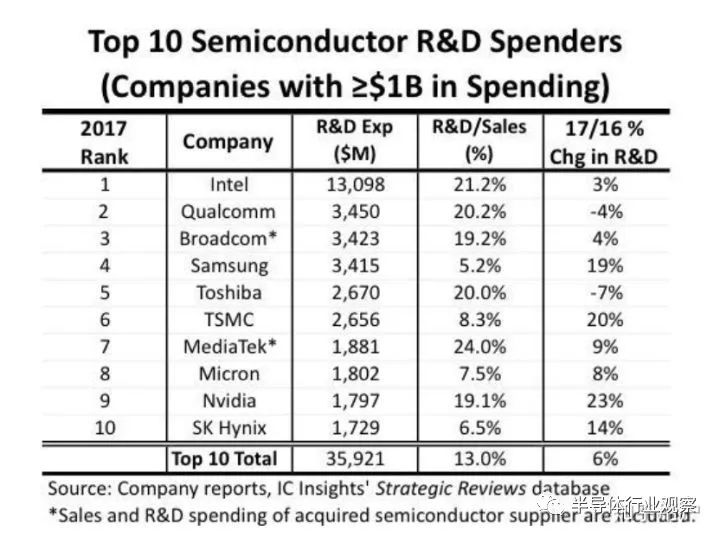

建立一条先进制程芯片产线需要大量的资金投入,而维持一条先进制程产线本身也需要大量的资金投入,因此需要保证产线尽可能满负荷运营才能实现有竞争力的盈利。所以需要保证有充足的订单,要想拿到订单又需要有领先的制程技术,领先的制程技术又需要大量的研发经费, 很多半导体厂商玩不起就玩不下去了。

生产运营包含提高良品率,提高生产效率,节约成本,事故预防等等,所以芯片制造不只是制造出来就可以,还需要以尽可能低的成本制造出来。

-

芯片制造

+关注

关注

9文章

607浏览量

28762

原文标题:你真的知道芯片制造有多难么?

文章出处:【微信号:iawbs2016,微信公众号:宽禁带半导体技术创新联盟】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

无人机智能巡检系统到底有哪些作用

带你领悟芯片制造到底有多难

带你领悟芯片制造到底有多难

评论