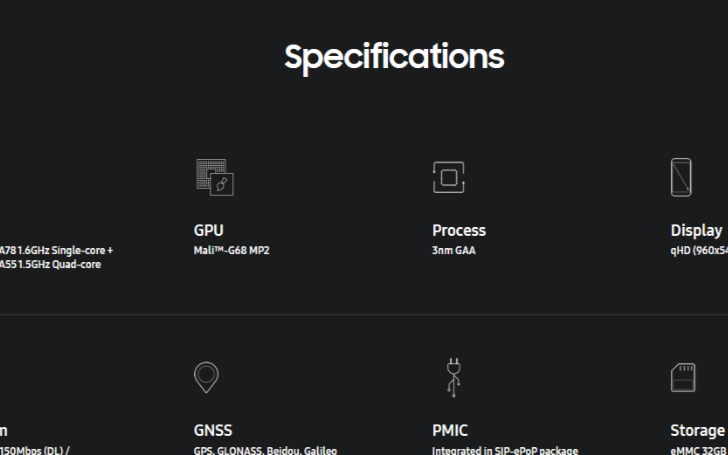

韩国三星电子于15日宣布在“Samsung Foundry Forum 2019 USA”上发布工艺设计套件(PDK)0.1版3nm Gate-All-Around(GAA)工艺“3GAE”。

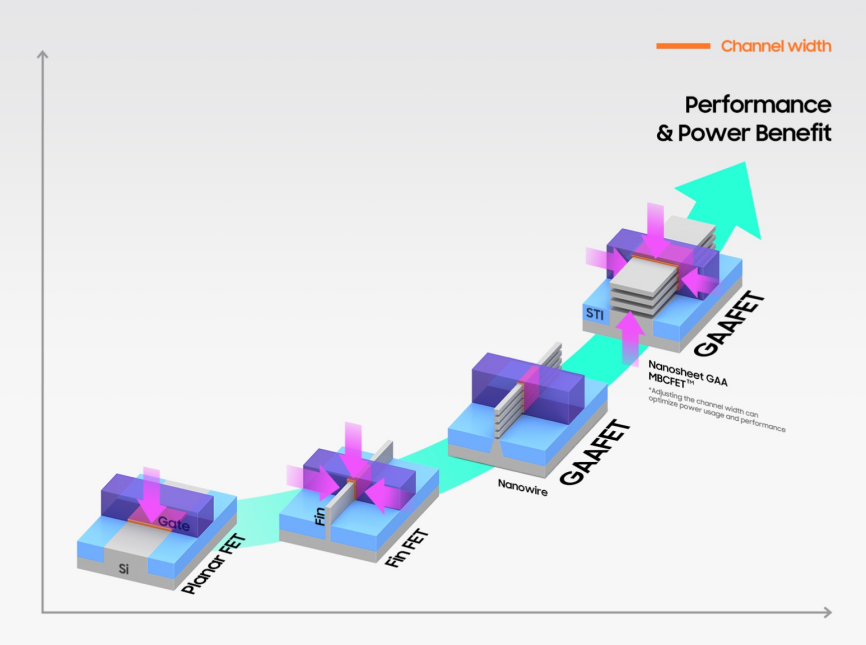

与7 nm工艺相比,3GAE可将芯片面积减少高达45%,降低50%的功耗或实现35%的性能提升。基于GAA的过程节点有望用于下一代应用,如移动,网络,汽车,AI和物联网。

3GAE的特点是采用GAA的专利变体“MBCFET(多桥通道FET)”而不是传统的GAA,该公司已经完成了测试车辆设计,并将专注于提高其性能和功率效率。

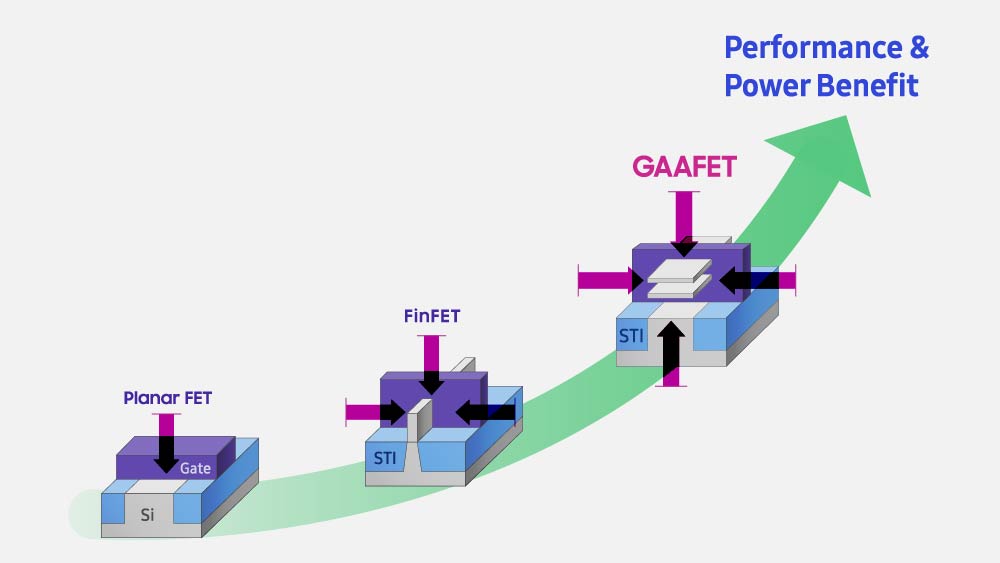

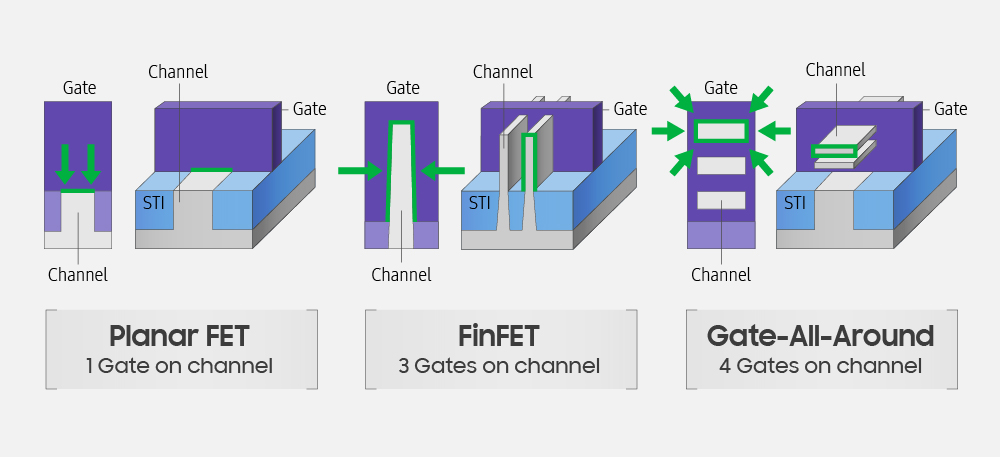

图:晶体管结构的转变

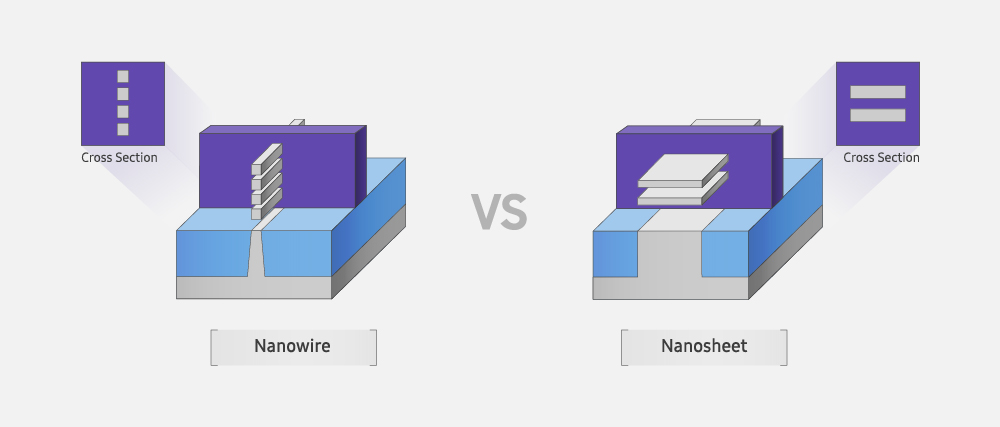

在传统的GAA中,由于沟道是nm线的形式,因为沟道薄且小,所以难以传递更多的电流,并且必须设计诸如增加堆叠数量的措施。它使用通道结构来排列nm片,增加了栅极和沟道之间的接触面积,并实现了电流的增加。

该公司声称它将彻底改变半导体行业,其中MBC FET已经小于4nm,并为第四次工业革命提供核心技术。

图:结构

根据该公司发布的工艺路线图,将使用极紫外(EUV)曝光技术制造4个7nm至4nm的FinFET工艺,然后使用EUV制造3nm GAA和MBCFET。而目前他们已经做到了!

该公司将在2019年下半年开始批量生产6nm工艺器件,同时完成4nm工艺的开发。5nm FinFET工艺的产品设计于2019年4月开发,也将于2019年下半年完成,并将于2020年上半年开始量产。开发28FDS,18FDS,1Gb容量的eMRAM也计划于2019年完成。

图:传统的GAA和MBCFET

-

三星电子

+关注

关注

34文章

15885浏览量

181616 -

EUV

+关注

关注

8文章

609浏览量

86380 -

芯片工艺

+关注

关注

0文章

13浏览量

7188

发布评论请先 登录

相关推荐

三星3nm良率仅20%,仍不放弃Exynos 2500处理器,欲打造“十核怪兽”

三星Exynos 2500芯片研发取得显著进展

可穿戴芯片进阶至3nm!Exynos W1000用上了面板级封装,集成度更高

三星电子发布为可穿戴设备设计的首款3纳米工艺芯片

三星首款3nm可穿戴设备芯片Exynos W1000发布

三星3nm芯片良率低迷,量产前景不明

台积电3nm工艺稳坐钓鱼台,三星因良率问题遇冷

三星展望2027年:1.4nm工艺与先进供电技术登场

台积电3nm产能供不应求,骁龙8 Gen44成本或增

消息称三星第二代3nm产线将于下半年开始运作

三星3nm移动应用处理器实现首次流片

三星电子开始量产其首款3nm Gate All Around工艺的片上系统

三星电子:加快2nm和3D半导体技术发展,共享技术信息与未来展望

三星电子澄清:3nm芯片并非更名2nm,下半年将量产

三星澄清:未采用MR-MUF工艺,持续创新引领HBM芯片技术

三星3nm工艺创新采用‘GAAFET结构’ 芯片面积减少45%

三星3nm工艺创新采用‘GAAFET结构’ 芯片面积减少45%

评论