随着物联网应用的兴起,对芯片低功耗的需求也会越来越多。分析几个关键的低功耗技术,对比通用的设计方法,未来会有更多低功耗架构的电路及方法出现。低功耗的需求一定是和应用相关,没有最低,只有最合适的。

1 引言

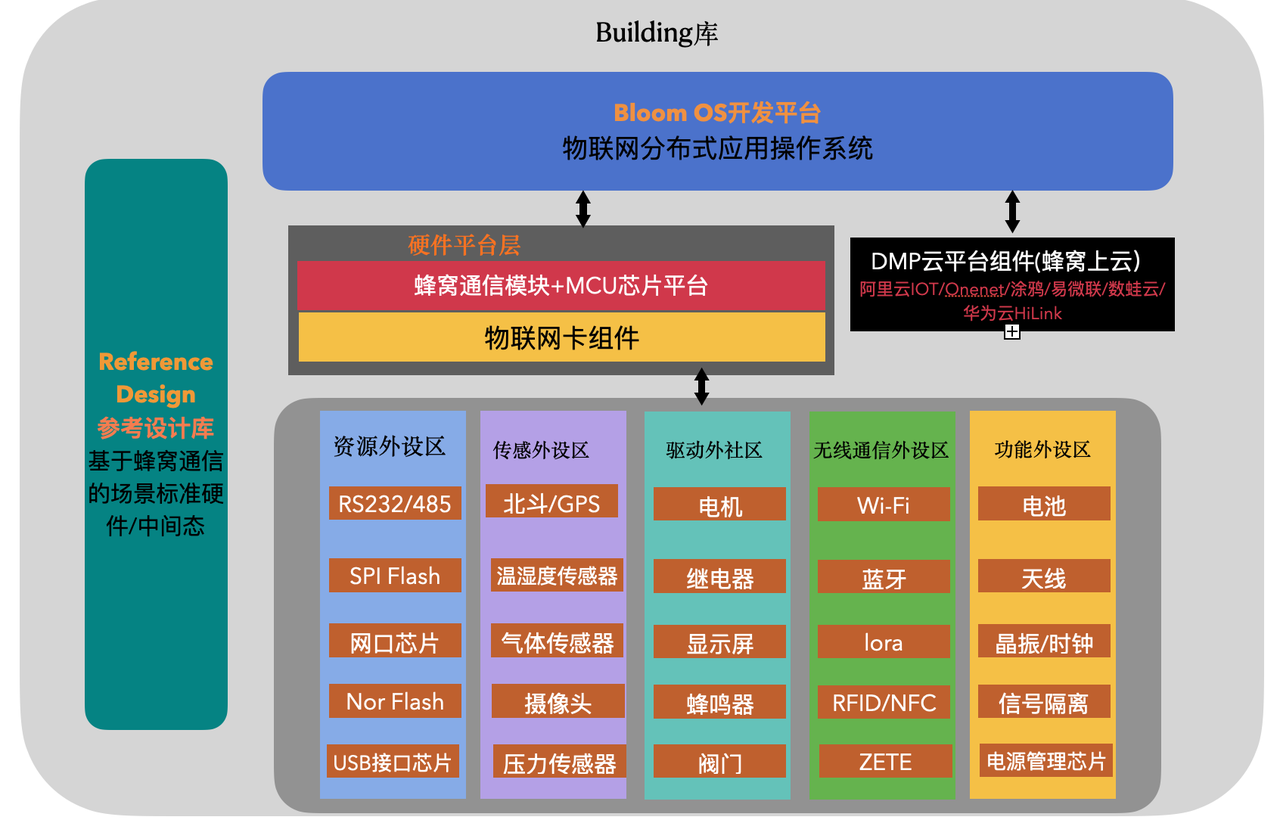

随着物联网和智能城市及智能电网的普及,MCU 的应用也迎来了井喷式的发展。目前国外大厂如ST、NXP、TI 等芯片公司占据 MCU 大部分的市场份额,且提供全系列芯片及产品来满足客户需求。对于国内公司来说,面临的压力和挑战是除了技术本身外面,构建 MCU 的生态系统也很重要。中国公司的优势在于中国是 MCU 应用最大的市场,本土企业更了解客户的需求和痛点。为此需要在架构创新性、产品的可靠性,低功耗设计及性能提升上做更多的努力。

2 MCU 技术

MCU 最初应用领域主要在工业控制和消费类市场,随着 MCU 需求量和应用的不断扩展,MCU 已全面向 SoC 方面发展,功能越来越强大,处理能力越来越强,外设和接口不断扩充。为了满足新的需求和高端应用市场,MCU 的架构也发生了很大的变化,从 51 core 向 AMR 内核发展,根据应用场景和需求不同,8/16/32 bit MCU 会并存一段时间,图 1 为 MCU 的应用方向向各种智能应用转换。

选择不同 bit MCU 要依据芯片的功能需求,性能需求,功耗要求及成本综合考虑。图 2 为各种 MCU 的占比图(资料来源:SIA/WSTS Semico Research Corp)。

从成本方面来讲,8 bit MCU 具有优势,可满足低端需求,而 32 bit MCU 因为提供更强大的运算处理能力,更快的速度已经成为高端 MCU 的标配。而高端 MCU 通常搭载 AMR cortex-M 处理器,配合丰富的外设接口及高可靠性,高性能的模拟模块,来提供满足市场及客户需求。MCU 中涉及的关键技术和问题非常多,从系统设计开始,如何定义系统架构,如何构建平台和MCU生态系统到数字电路设计;从工艺的选择到模拟电路的设计,从可靠性设计到低功耗设计;从应用创新到满足客户各种需求 。每个方面都对设计公司提出很高的挑战。

本文仅从低功耗设计的角度研究 MCU 在低功耗设计方面的一些技术挑战和方向。

3 MCU 的低功耗设计

随着物联网的兴起,各种可穿戴设备都需要电池供电,MCU 的要求除了丰富的功能模块支持和高性能指标之外,低功耗也成为一个非常重要的课题。特别是可穿戴设备大多采用电池供电,希望待机时间很长,所以低功耗设计的重要性就特别凸现。MCU 的低功耗设计不仅需要保证在正常模式下,芯片的功耗要低,而且需要合理配置工作模式,让芯片能够尽可能的省电,即大多数情况下,芯片处于省电模式下,尽可能延长电池的使用寿命。图 3 是一般 MCU 芯片的工作模式,为了省电,一般设计仅仅在需要工作时将必要的模块打开,而大多数情况模块处于 Sleep 模式,也即尽量降低处于 Normal 模式的时间。

低功耗的设计涉及正常模式的低功耗设计及睡眠模式下的低功耗设计两个方面。这两方面对于低功耗设计都非常重要,下面分别进行分析。

3.1 Normal 模式的低功耗设计

MCU 芯片的周期从 Sleep 模式进入 Normal 模式进行数据处理,数据处理结束之后立即进入 Sleep 模式。一般 MCU 还有一个 Hold mode,功耗比 Normal 模式低,与系统定义相关,即根据需要选择性的开关一些模块并保持一定的状态。

Normal 模式下的功耗包含数字动态功耗和以模拟为主的静态功耗。

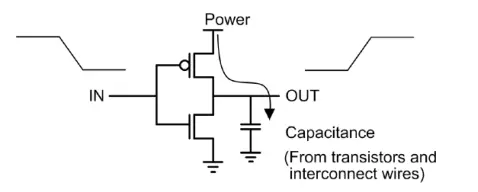

数字动态功耗的表达式为式(1)

P=α×Vdd2×f×Cl (1)

其中,Vdd 为数字工作电压,f 为数字工作频率,Cl 数字模块的负载,而α是开关工作的比率。在 Normal 模式下,数字工作在低频及采用深亚微米工艺使其 load 更小,尽量降低开关的次数会大大降低数字部分的动态功耗。但是工作电压的降低会带来速度的降低,会降低数字电路的抗干扰性能。图 4 是不同模块根据系统定义和需求工作在不同的电源电压下的示例。 采用 Clock gated 技术[1](图 5)可以大大降低功耗,使得数字模块仅仅在需要工作时工作。另外降低系统频率也会优化功耗,但是会带来处理速度的下降。所以数字动态功耗的优化需要结合系统需求来进行。一般数字模块通过合理的分配不同模块工作在不同的电源电压下,并且采用合理的门控时钟方案和选择合适的时钟,以实现功耗的最优化设计。

除了数字动态功耗外,模拟模块的设计也要求低功耗。在 Normal 模式下,模拟的模块如电源管理模块,Bandgap Reference 及 Voltage Regulation,在保证性能的情况下,尽可能降低模拟电路的功耗(图 6)。

3.2 Sleep 模式下的低功耗设计

MCU 在睡眠模式下,为了得到低功耗,一般需要在如下几个方面进行设计优化,系统级,工艺级,模拟及数字模块设计。如图 7 所示。

MCU 低功耗设计离不开工艺的支持,工艺的选择对 MCU 的低功耗影响很大,一般 Foundry 厂家都提供 Low power 或 Low leakage 的工艺。芯片进入睡眠模式后,数字电路大部分处于 power down的状态。如果工艺选择合适,数字电路在睡眠模式的漏电流就很小,芯片才可能实现低功耗的模式。

工艺越先进,漏电流越大。为此需要采用 Low leakage 的工艺来进行低功耗的设计。器件的漏电流由 Gate 漏电流(由通过 Gate 氧化层的载流子隧穿电流),深亚微米工艺下,Gate 氧化层厚度减小,进入通过氧化层的电场增强,隧穿效应比较明显。GIDL 电流,源漏的穿通电流,热载流子效应及反向PN结的遂穿电流都会导致漏电流的增加。所以工艺的评估非常重要[2](图 8)。

另外进入 Sleep 模式后,整个系统的功耗控制方案需要提前评估,是否需要 power gate 的控制,即断开模块的电源,彻底断电。或者需要规划系统在进入 Sleep 模式后,各个模块的供电是如何考虑的?是否需要 DC-DC 或 LDO 供电,供电的电压是多少?系统电源的策略对最终的低功耗有很大的影响。 比如采用 DC-DC 供电就比直接采用 LDO 更省电,但是 DC-DC 带来的电源波动对电路的影响需要结合系统需求来决定,也可以采用 DC-DC 加 LDO 的方式,但会带来面积上的代价等,这些都需要综合考虑。 另外一个考虑是进入 Sleep 模式后,时钟的频率的大小,是来自 RC OSC 或 OSC 32k 等。

上面两方面确定之后,就需要考虑低功耗的模拟及数字电路设计,对于模拟模块来说,提供低功耗的 LDO 和时钟及复位模块直接决定于 Sleep 模式下的 MCU 功耗,LDO 作为供电模块,虽然在 Sleep 模式下驱动电流很小,但其本身的功耗要尽可能的小,LDO 的参考 Bandgap 也同样需要低功耗的设计,一般情况下,Sleep 模式对 LDO 的电压精度要求不高,所以使得低功耗的设计成为可能。时钟模块需要结合系统定义,确定低功耗模式下是提供精准的 OSC 32k 时钟还是 RC OSC 的时钟就可以满足要求。另外模拟也需要提供 Reset 模块来监控外部电源的情况,如果电源电压太低,也需要及时输出相应的指示信号。

对于低功耗模拟电路来说,从图 9(gm/Id 图)[3]中可以看到,如果模拟电路工作在低功耗区域,则模拟模块需要工作在亚阈值区。亚阈值区模拟 MOS 管的电流和 VGS 的关系如式(2),VGS 输入非常接近 Vth。在亚阈值区间,MOS 管的电流和 VGS 成指数关系[4]。

Id=Is×eVGS/(n×KT/q)(2)

对于数字电路的模块,进入 Sleep 模式后,常开的逻辑电路一般对于时序要求不高,可以采用适当降低其供电电压来降低功耗,采用尽可能低的时钟来保持一定的工作状态。另外一个非常重要的模块是 RAM 的设计,RAM 在 Sleep 模式后,一部分会 power down。另外一部分电路需要处于保持模式,来存储一定的数据,既不会读也不会进行写操作,只要保持状态即可。而 RAM 的电流占到数字电流很大的比列,通常采用的 RAM 功耗降低的方法有降低 RAM 的工作电压或采用特殊结果的 RAM 电路来降低功耗。

4 结语

MCU 的低功耗设计是 MCU 芯片非常核心的技术,也是各家 MCU 进行性能指标对比最关键的一个环节。在 MCU 的低功耗设计中,涉及从芯片工艺﹑系统设计到模拟及数字实现的方方面面。随着物联网应用的兴起,对低功耗的需求也会越来越多,本文提到的几个关键的低功耗技术是一些比较通用的设计方法,未来也会有更多低功耗架构的电路及方法出现,但不论怎样,低功耗的需求一定是和应用相关的——没有最低,只有最合适的。

-

芯片

+关注

关注

457文章

51356浏览量

428310 -

集成电路

+关注

关注

5396文章

11644浏览量

363733 -

单片微处理器

+关注

关注

0文章

3浏览量

6564

原文标题:一种低功耗 MCU 芯片的设计方法

文章出处:【微信号:appic-cn,微信公众号:集成电路应用杂志】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

国产LORA 低功耗广域网内置MCU ASR6601开发资料

物联网学习路线来啦!

低功耗SOC芯片的优势

物联网系统中TCP低功耗产品长连接状态下降低功耗功能的实现方案

引领智能未来:英锐恩科技的国产低功耗单片机ENMCU

物联网系统中音频方案的“大脑”_语音芯片

国产化低功耗低延时广覆盖物联网无线通讯方案_LAKI芯片

物联网应用的兴起 对芯片低功耗的需求会越来越多

物联网应用的兴起 对芯片低功耗的需求会越来越多

评论