最近中国射频芯片产业存在的诸多不足,再次引起行业的广泛关注。这是知乎网友Chris之前回答一位网友关于射频芯片设计的难题有哪些的问题,觉得有一定的讨论价值及通用性。

射频芯片设计面临的难题是非常多的,有设计者理论及经验方面的主观因素,最大的难题还是工艺及封装的客观限制因素。

首先说一下主观因素吧,射频芯片设计需要的理论知识真的是非常多,很多设计理论甚至被人认为玄乎,而且射频芯片的设计存在各种指标的折中均衡,什么样的折中是最佳的?怎样折中是取决于产品的实际应用要求,没有定论,所以经验的积累也算是一个难题吧。再者很多射频芯片的指标要求都是要挑战工艺极限,这就需要很多创新性的电路结构,例如噪声抵消啊、交调分量抵消啊、为了提高功放效率采用的动态偏置啊,有时为了降低功耗也是想尽了办法,各种电流复用。

关键的还是工艺及封装的物理限制或者模型的不准确性导致的难题。射频芯片最重要的指标是噪声系数和线性度,这两个指标和工艺完全相关,例如cmos工艺衬底上就会耦合过来各种噪声干扰,cmos器件的线性度也很差,这种难题是硬伤,没办法解决,只能通过合适的电路结构或者采取一些无法定量分析的隔离措施来缓解问题,这就存在很多不确定性了。

其次,射频电路随着频率的升高,对寄生参数越来越敏感,大的寄生电阻、电容会使电路的性能降低到无法容忍的地步,那么如何准确的评估这些寄生参数的量就是一个极大的难题,这里面涉及到器件的精确射频模型建模和版图中寄生参数的精确提取。器件的射频精确模型是业内的一大难题,频率越高偏差会越大,还有一些器件特性难以建模,例如亚阈值区域特性,大信号条件下的高阶非线性特性,各类噪声特性的准确建模,这些模型的问题都会带来仿真结果与实际产品之间的差异,器件模型近年来还是有了长足发展了,成熟工艺厂提供的模型在射频频段还是相对比较准确了,微波及毫米波频段会差异大些。另外一个难题就是版图寄生参数提取的准确性和电磁仿真的建模精度问题,版图寄生参数通常只是提取寄生的电阻和耦合电容,精度也非常有限,这些寄生参数对电路的影响往往又是致命的,可能会使高频增益严重降低,噪声急剧恶化,匹配完全偏离设计,甚至带来稳定性问题;而且工作频率升高以后分布寄生参数对电路影响的评估变得极不准确,电磁耦合干扰的问题会很严重,这时就需要电磁仿真工具来进行评估了,电磁仿真严重依赖于晶圆上各层材料的建模,这个模型非常难建的准确,特别是衬底的模型,通常都会简化很多因素来建立一个相对简单实用的模型,其次电磁仿真本身就存在精度问题,这都导致了版图对电路性能影响的评估存在偏差。

很多时候能够通过一些手段来评估分布寄生参数或者电磁耦合对射频芯片电路的影响,可是对电路版图却束手无策,没办法优化,或者怎么优化都没什么本质性的改善,这才是让人头疼的事情。

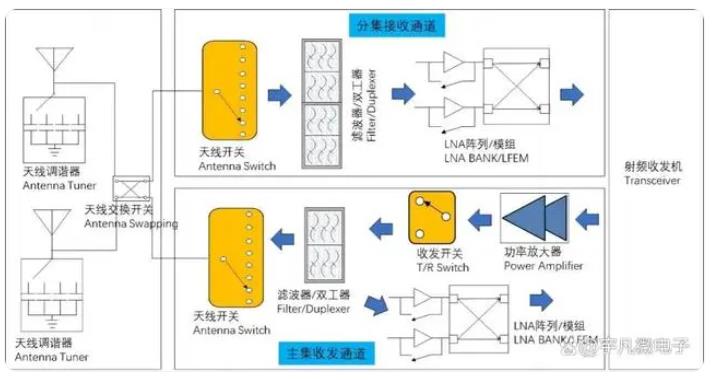

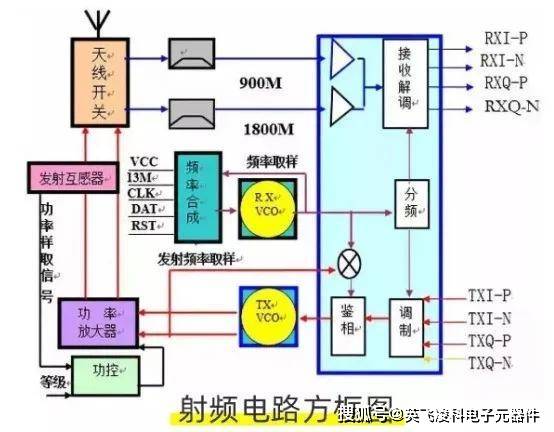

以上所说的基本都还是单个功能模块电路在设计上会遇到的难题,到整个复杂芯片的总版图及封装设计阶段还有很多其它难题。例如完整的transceiver包含射频前端、锁相环、ad采样、发射上变频通道及射频功率放大器,很多部分都是数模混合电路,存在各个部分之间的相互干扰,特别是通过衬底、电源、地的干扰和电磁耦合干扰,这些因素的评估和分析真的可以上升为玄学了,通常是依赖多次的流片测试来评估了,因为基本没办法定量分析。还有一个难题是射频芯片的esd设计,小小的esd二极管带来的寄生电容也可能是致命的,太小的esd二极管又满足不了抗静电要求,总之就是矛盾。

射频芯片设计完成以后的封装影响也是一大难题,小小的一根封装引线就是1nH以上的电感,这些电感对射频芯片的影响实在是太大了,在成本可控的前提下尽量采用先进的封装形式,减少封装带来的引线电感。

-

封装

+关注

关注

126文章

7901浏览量

142954 -

射频芯片

+关注

关注

976文章

412浏览量

79617

原文标题:行业 | 射频芯片设计有哪些难题?

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

射频功放芯片选型原则

射频芯片的工作原理和用途

基带芯片和射频芯片的关系

中国AI芯片行业,自主突破与未来展望

人工智能芯片在先进封装面临的三个关键挑战

奇捷科技研发VP袁峰博士发表主题演讲,助力企业攻克芯片设计难题

疯狂内卷下,2024射频芯片看这篇

中国射频芯片设计面临哪些难题?

中国射频芯片设计面临哪些难题?

评论