讨论在标准 0.18μm CMOS 逻辑平台上加入一次性编程单元(OTP Cell)后,工艺所面临的问题。由于 OTP Cell 的设计尺寸远小于 0.18μm 技术代的设计要求,导致用传统工艺对 OTP Cell 中具有高纵横比的间距进行填充时,会出现空洞。该空洞贯通前后接触孔(CT),使得后续在沉积 TiN 时,TiN 会残留在空洞侧壁上,使相邻接触孔短路,从而导致 OTP 失效。为了解决这个问题,从多个方面进行了方案设计,包括硼磷硅玻璃(BPSG)中硼(B)和磷(P)的浓度,BPSG 的厚度,回流温度以及在 BPSG 之前先沉积一层高密度等离子体氧化物(HDP USG)。实验结果表明,只有在 BPSG 之前先沉积一层 HDP USG 的工艺方案才是有效的,才可以消除空洞,从而消除 TiN 残留物。同时,器件性能不受影响,并实现了高良率。

1 引言

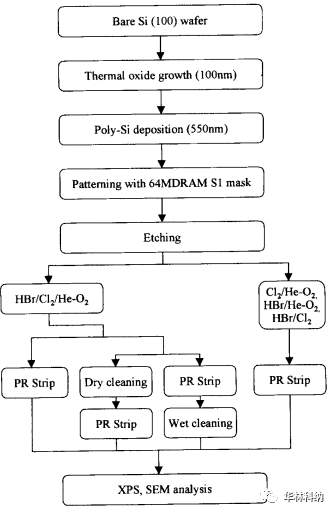

在集成电路工艺中,0.18μm 制程作为一种低成本工艺制程,目前还是被大量、广泛运用于制造一些集成电路产品,尤其是一些中低端产品或对线宽尺寸不是很敏感的领域如汽车电子。通常的 0.18μm 制程,接触孔 CT(Contact)的形成工艺是,首先,生长一层刻蚀终止层(Etching Stop Layer),接着沉积掺有元素硼(B)和磷(P)的硼磷硅玻璃 BPSG,在高温回流工艺后再沉积一层等离子体增强型氧化层(PE-TEOS),然后用化学机械抛光法进行表面平整化,接着进行干式刻蚀形成接触孔。紧接着在接触孔四周侧壁上沉积黏结层 Ti/TiN,随后填埋钨(W)作为连接导体。这对标准的 0.18 μm 技术代设计准则来说,工艺很成熟,不会有任何问题,但如果在这个技术平台上加入一些其他的器件或工艺如 OTP(One Time Program)工艺,为了降低成本,提高产品竞争力,我们通常超越设计准则,使得这些器件或 OTP 尺寸做的非常小,不可避免地造成高纵横比间距,这会带来一些工艺上的问题。本论文讨论的就是在 0.18μm 通用平台的基础上加入一个尺寸非常小的 OTP 单元后工艺上所面临的问题和挑战,以及相应的解决方案。

图 1 为我们使用的 OTP Cell,覆盖浮栅的相邻 SAB(金属硅化物阻挡层)的间距非常小,只有 0.28μm,而标准的 0.18μm 工艺平台,相邻 SAB 的最小间距为 0.42μm。这么小的间距,加上浮栅高度和特别为 OTP 工艺加厚的 SAB 厚度,形成了很高的纵横比间距。如果在刻蚀终止层上直接沉积 BPSG,很容易导致间距顶已被 BPSG 合拢,但下面还没填实,出现空洞,这些空洞会前后贯通,尽管接下来有 BPSG的高温回流工艺,但该回流是一个微流动,有别于通常的流体流动,所以,这个空洞不会因为 BPSG 的高温回流而消失。接触孔侧壁在形成 Ti/TiN 黏结层的过程中,采用的是化学气相沉积(CVD)的形成方式,所以 TiN 同时也会在空洞的侧壁上沉积,由于空洞是前后贯通的,导致其侧壁上的 TiN 贯通前后接触孔而造成 Bit Line 短路,从而使芯片失效,如图 2 所示,其中 SEM 俯视图显示前后接触孔被连起来了,TEM 剖面图所示空洞侧壁上有残留物,SMIS 表明此残留物含 Ti 和 N 元素,与接触孔侧壁上的黏结层是同一种物质,即 TiN。

2 实验方案

为了解决高纵横比间距下的 TiN 残留物问题,我们从多个角度出发,改变工艺条件进行了研究,首先从物理层面确定工艺条件,然后从器件电性和芯片良率层面进一步验证该工艺条件的有效性。我们所用的样品都取自于全工艺流程的晶圆,采用的是在标准的 0.18μm CMOS 工艺上加入 OTP 制程。这些晶圆除了变化的工艺步骤外,其他的工艺完全相同。表 1 所列为实验方案,其中方案编号 #1 为当前工艺,作为对比的控制组;我们分别从 BPSG 中掺杂的 B和 P 浓度,BPSG 厚度,BPSG 回流温度设计了编号 #2~#4 的实验方案,其目的是增加 BPSG的流动性,使其回流过程中填补其沉积时出现的空洞,为了控制整个厚度,以减少对后续化学机械研磨(CMP)和接触孔刻蚀工艺的影响,我们同时调整了方案编号 #3 和 #4 中 TEOS 的厚度。方案编号#5 在 BPSG 之前,我们先沉积了一层高密度等离子体氧化物(HDP USG),这主要是考虑了 HDP 卓越的填洞能力,尤其在高纵横比间距的情况下。

3 实验结果与讨论

表 2 为实验结果,图 3 为相应的 SEM 俯视图,在所设计的方案中只有方案 #5 才能实现无 TiN 残留物的目标。表中“严重程度”表示残留物的多少,最严重的情况是前后两个接触孔已被空洞侧壁上的 TiN 残留物短路了。BPSG 的回流特性对掺杂的 B 和 P 的浓度非常敏感[1],浓度稍有升高,回流温度降低明显,BPSG 的回流效果就越好,但浓度并非越高越好,P 高了,会影响 BPSG 的稳定性和可靠性,B 高了抗潮能力会减弱。在标准 0.18μm 工艺中,B/P 通常在 4.6%/3.5% 左右。BPSG 的回流性能还跟温度有关,温度越高,回流性能越好。在方案 #2 中,B/P 浓度增加到 4.9%/4.4%,回流温度提升至 700℃,双管齐下改善回流性能,在回流平坦化过程中使空洞消失,从而消除 Ti N残留物,然而,实验结果表明,尽管本方案较当前工艺 #1 有改善,但仍然存在 TiN 残留物。而且,器件性能因过高的回流温度而彻底改变,阈值电压 Vt 相较当前工艺 #1,NMOS漂了 25%,而 PMOS 更是漂了 40%。方案 #3,BPSG 的厚度从 2 k 增加到 3 k,以确保 BPSG 在回流平坦化过程中有足够的量来填充空洞使其消失。从而消除 TiN 残留物,但实验结果显示,TiN 残留物状况未见明显改善,说明空洞依然存在。为了改善回流特性,同时尽量减少回流温度对前端器件性能的影响,方案 #4 在方案 #3 的基础上,回流温度略微增加至 650℃。同样,该方案无法消除空洞,TiN 残留物也未见其明显好转。以上方案表明,通过 BPSG 厚度,B/P 浓度以及回流温度来解决 TiN 残留物,收效甚微,必须另辟蹊径。

众所周知,用高密度等离子体法(HDP)沉积氧化物能实现非常好的台阶覆盖(Step coverage),特别适合填充高纵横比间隙,具有卓越的填洞能力[2]。在 HDP 氧化物形成过程中,通过调节其刻蚀(Etch)和沉积(Deposition)之比来实现其最佳的填充效果,达到消除空洞的目标。然而,HDP 中含有大量的离子,同时,通过溅射(Sputter)来实现的刻蚀,也能产生大量的电子、缺陷,这些离子、电子、缺陷对 OTP 的数据保持(Data Retention)是有害的。为了消除空洞,我们在方案 #5 中用了 2 k 的 HDP 氧化物,该 HDP 氧化物先于 BPSG 沉积。在沉积时,特别优化了刻蚀和沉积之比,以尽量减少离子、电子、缺陷对 Data Retention 的影响。另外,在该方案中,我们把 BPSG 增加到 3 k,同时降低 TEOS 的厚度到 6 k,以保持总厚度不变。

实验结果表明,空洞没有了,空洞侧壁上的 TiN 残留物也随之消失了,如图 3 所示。在电性层面,我们对晶圆进行了测试,结果显示,无论是 MOS 器件的性能(Ids,Vt 等),还是接触孔的电阻值,都与当前工艺一致。良率方面,由于最主要的 Data Retention 性能未见下降,所以得到了很高的良率。这充分说明,方案 #5 是有效的。用该方案作为我们生产标准后,从出货的几十万片晶圆数据来看,再一次证明该方案是非常成功的。

4 结语

本文讨论的是标准 0.18μm CMOS 逻辑平台上引入了超越规则的 OTP Cell 后,工艺所面临的问题。用传统工艺对 OTP Cell 中的高纵横比间距进行填充时,会留下贯通前后接触孔的空洞,在接触孔沉积 TiN 时,TiN 同样会残留在空洞侧壁上,使相邻接触孔短路,从而导致 OTP 失效。为了解决这个问题,我们从 BPSG 中 B/P 的浓度,BPSG 厚度,回流温度,以及在 BPSG 之前先沉积一层 HDP USG 的方式进行了多个方案设计。实验结果表明,只有在 BPSG 之前先沉积一层 HDP USG 的工艺方案才是有效的,才可以消除 TiN 残留物,同时,器件性能不受影响,并实现了高良率,以此为量产工艺条件生产出的几十万片晶圆数据进一步验证了该方案的有效性和可靠性。

-

集成电路

+关注

关注

5396文章

11646浏览量

363807 -

Tin

+关注

关注

0文章

4浏览量

7293

原文标题:高纵横比间距下 TiN 残留物的解决方案

文章出处:【微信号:appic-cn,微信公众号:集成电路应用杂志】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

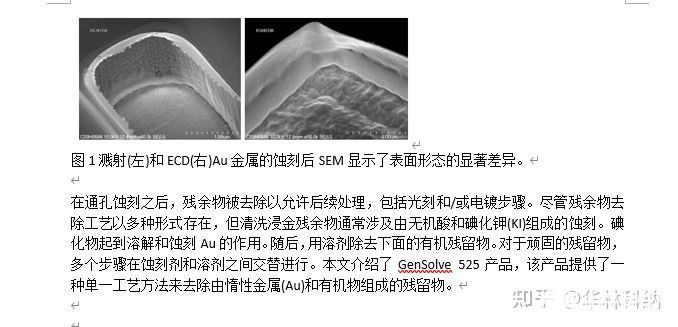

多晶硅蚀刻残留物的的形成机理

蚀刻后残留物和光刻胶的去除方法

【已解决】FPGA的TQFP封装焊接后引脚间留有白色松香残留物...

U1252A交流电压残留物

一文看懂污染物残留物对PCB点焊的影响

印刷电路板上焊剂残留物会造成哪些危害性

农药残留物检测仪可快速检测出农药残留问题

刻蚀后残留物的去除方法

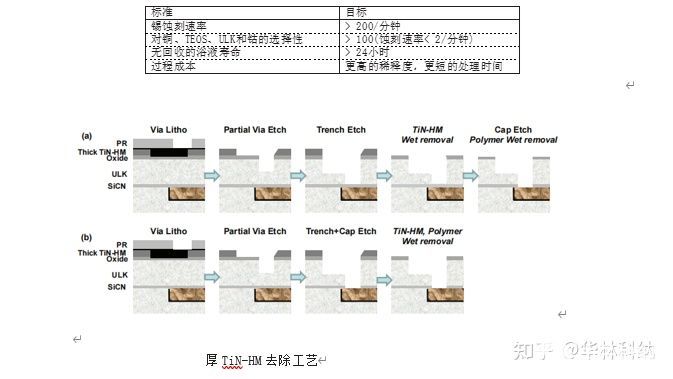

TiN硬掩模湿法去除工艺的介绍

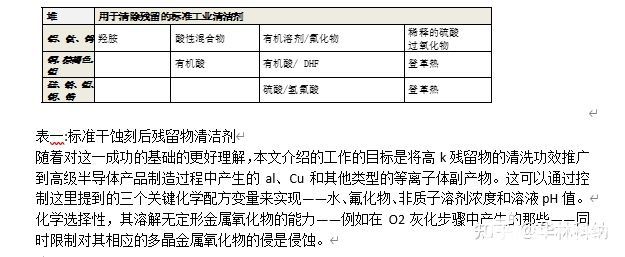

适用于清洁蚀刻后残留物的定制化学成分(1)

PCBA残留物的影响及清洗,助焊剂残留物怎么样清除

锡膏焊接后残留物如何清洗?

集成电路 | 高纵横比间距下 TiN 残留物的解决方案

集成电路 | 高纵横比间距下 TiN 残留物的解决方案

评论