同步动态随机存取内存(synchronous dynamic random-access memory,简称SDRAM)是有一个同步接口的动态随机存取内存(DRAM)。通常DRAM是有一个异步接口的,这样它可以随时响应控制输入的变化。而SDRAM有一个同步接口,在响应控制输入前会等待一个时钟信号,这样就能和计算机的系统总线同步。时钟被用来驱动一个有限状态机,对进入的指令进行管线(Pipeline)操作。这使得SDRAM与没有同步接口的异步DRAM(asynchronous DRAM)相比,可以有一个更复杂的操作模式。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

SDRAM

+关注

关注

7文章

459浏览量

57862 -

计算机

+关注

关注

19文章

7841浏览量

93493 -

内存

+关注

关注

9文章

3238浏览量

76528

发布评论请先 登录

相关推荐

热点推荐

FPGA零基础学习:SDR SDRAM驱动设计实用进阶

实战应用,这种快乐试试你就会懂的。话不多说,上货。SDR SDRAM驱动设计实用进阶 本篇实现基于叁芯智能科技的SANXIN -B01 FPGA开发板,以下为配套的教程,如有入手开发板,可以登录官方

发表于 03-27 17:09

FPGA读写SDRAM的实例和SDRAM的相关文章及一些SDRAM控制器设计论文

本文档的主要内容详细介绍的是FPGA读写SDRAM的实例和SDRAM的相关文章及一些SDRAM控制器设计论文主要包括了:

发表于 12-25 08:00

•58次下载

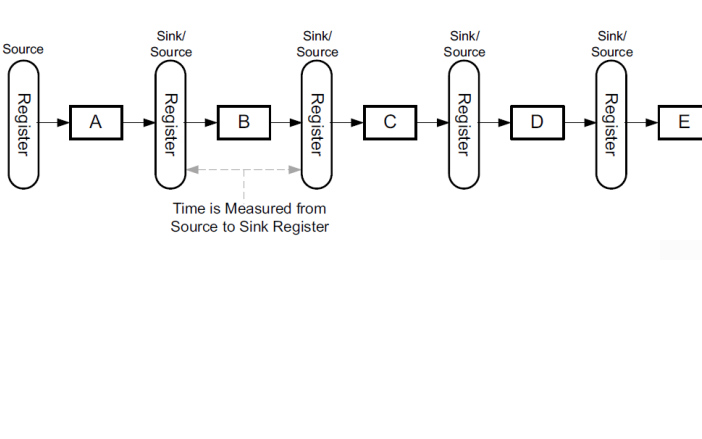

FPGA学习教程之硬件设计基本概念

关于FPGA架构和基本组成《FPGA学习–架构和基本组成单元(一)》 ,下面参考Xilinx Vivado官方文档学习硬件设计的基本概念。

发表于 12-25 17:34

•23次下载

时序分析和时序约束的基本概念详细说明

时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

发表于 01-08 16:57

•28次下载

FPGA设计中时序分析的基本概念

时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

FPGA进阶教程:SDRAM的基本概念介绍

FPGA进阶教程:SDRAM的基本概念介绍

评论