ROM所存数据稳定,断电后所存数据也不会改变;其结构较简单,读出较方便,因而常用于存储各种固定程序和数据。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22508浏览量

639415 -

ROM

+关注

关注

4文章

579浏览量

89385 -

IP核

+关注

关注

4文章

345浏览量

52111

发布评论请先 登录

相关推荐

热点推荐

FPGA IP核的相关问题

我用的是xinlinx spartan6 FPGA,我想知道它的IP核RAM是与FPGA独立的,只是集成在了一起呢,还是占用了FPGA的资源

发表于 01-10 17:19

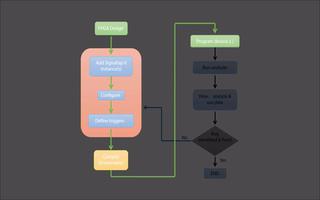

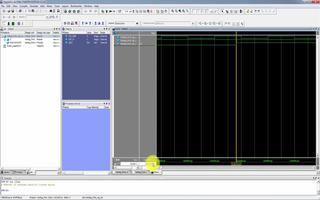

【锆石A4 FPGA试用体验】IP核之ROM(二)创建ROM IP核

前面建好了mif文件,下面就要创建ROM IP核了。首先,我们新建一个工程。菜单栏:Tools --> MegaWizardPlug-InManager ,点击“Next”选择ROM的

发表于 09-25 09:38

【锆石科技】很好的FPGA入门培训视频-《HELLO FPGA》课程(免费下载)

02集: Verilog的关键问题解惑软件工具篇:第01集: Quartus软件使用讲解第02集: ModelSim

发表于 03-15 15:30

FPGA零基础学习:IP CORE 之 ROM设计

,学习FPGA设计方法及设计思想的同时,实操结合各类操作软件,会让你在技术学习道路上无比的顺畅,告别技术学习小BUG卡破脑壳,告别目前忽悠性的培训诱导,真正的去学习去实战应用。话不多说,上货。 IP

发表于 03-13 15:46

IP CORE 之 ROM 设计- ISE 操作工具

不多说,上货。IP CORE 之 ROM 设计- ISE 操作工具本篇实现基于叁芯智能科技的SANXIN -B02 FPGA开发板,如有入手

发表于 04-07 20:09

FPGA之软件工具篇:PLL IP核的使用讲解

该篇不仅讲解了如何使用Quartus II软件、ModelSim和SignalTap II软件,还讲解了PLL、

FPGA之软核演练篇:内置IP核之Interval Timer的应用实战讲解

软核演练篇包含了哪些内容:该篇以什么是软核、什么是Qsys、如何构建一个Qsys系统为切入点,在该基础上进一步介绍了Nios II处理器的体系结构、Qsys丰富多彩的内置

FPGA之软核演练篇:内置IP核之Interval Timer的理论原理讲解

软核演练篇包含了哪些内容:该篇以什么是软核、什么是Qsys、如何构建一个Qsys系统为切入点,在该基础上进一步介绍了Nios II处理器的体系结构、Qsys丰富多彩的内置

FPGA之软核演练篇:内置IP核之System ID的讲解

软核演练篇包含了哪些内容:该篇以什么是软核、什么是Qsys、如何构建一个Qsys系统为切入点,在该基础上进一步介绍了Nios II处理器的体系结构、Qsys丰富多彩的内置

FPGA之软件工具篇:ROM IP核的使用讲解

FPGA之软件工具篇:ROM IP核的使用讲解

评论