PS/2接口是输入装置接口,而不是传输接口。所以PS2口根本没有传输速率的概念,只有扫描速率。在Windows环境下,ps/2鼠标的采样率默认为60次/秒,USB鼠标的采样率为120次/秒。较高的采样率理论上可以提高鼠标的移动精度。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1631文章

21806浏览量

606717 -

WINDOWS

+关注

关注

4文章

3584浏览量

89483 -

IP核

+关注

关注

4文章

331浏览量

49689

发布评论请先 登录

相关推荐

【锆石A4 FPGA试用体验】锆石科技-A4 FPGA开发板开箱鉴赏-您将得到的是一门技术

/jishu_1153091_1_1.html锆石科技-A4 FPGA开发板 板载六枚高品质7段数码管锆

发表于 07-29 16:33

【锆石A4 FPGA试用体验】初识锆石A4 FPGA开发板

` 本帖最后由 jinglixixi 于 2017-8-3 11:14 编辑

期待中的锆石A4 FPGA开发板终于如期而至了,欣喜中快速

发表于 08-03 11:12

锆石FPGA A4_Nano开发板视:PS/2外设IP核的应用

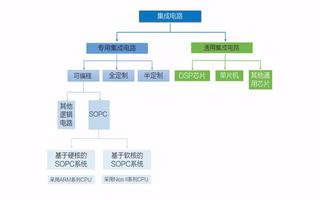

IP核有三种不同的存在形式:HDL语言形式,网表形式、版图形式。分别对应我们常说的三类IP内核:软核、固核和硬核。这种分类主要依据产品交付的

锆石FPGA A4_Nano开发板视频:DA外设IP核制作

IP主要分为软IP、固IP和硬IP。软IP是用Verilog/VHDL等硬件描述语言描述的功能块,但是并不涉及用什么具体电路元件实现这些功能

锆石FPGA A4_Nano开发板视频:LED的IP核应用

利用IP核设计电子系统,引用方便,修改基本元件的功能容易。具有复杂功能和商业价值的IP核一般具有知识产权,尽管IP

锆石FPGA A4_Nano开发板视频:DA外设IP核定制

IP核有三种不同的存在形式:HDL语言形式,网表形式、版图形式。分别对应我们常说的三类IP内核:软核、固核和硬核。这种分类主要依据产品交付的

锆石FPGA A4_Nano开发板视频:定制最基本LED的IP核

IP主要分为软IP、固IP和硬IP。软IP是用Verilog/VHDL等硬件描述语言描述的功能块,但是并不涉及用什么具体电路元件实现这些功能

锆石FPGA A4_Nano开发板视频:什么是Qsys?如何构建一个Qsys系统?

视频中进一步介绍了Nios II处理器的体系结构、Qsys丰富多彩的内置IP,以及Avalon总线接口规范,然后我们又以Avalon总线接口规范为基础,进一步定制了开发板所有

锆石FPGA A4_Nano开发板视频:VGA外设的IP核定制

IP核有三种不同的存在形式:HDL语言形式,网表形式、版图形式。分别对应我们常说的三类IP内核:软核、固核和硬核。这种分类主要依据产品交付的

锆石FPGA A4_Nano开发板视频:PS/2外设IP核的定制

锆石FPGA A4_Nano开发板视频:PS/2外设IP核的定制

评论