声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1626文章

21669浏览量

601866 -

uart

+关注

关注

22文章

1227浏览量

101176 -

IP核

+关注

关注

4文章

326浏览量

49429

发布评论请先 登录

相关推荐

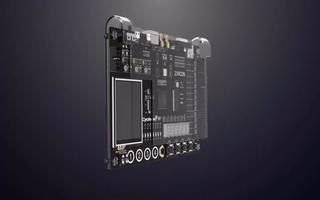

【锆石A4 FPGA试用体验】锆石科技-A4 FPGA开发板开箱鉴赏-您将得到的是一门技术

全家福开启说明书与光盘包装盒,包含以下附件:锆石科技-A4 FPGA开发板引导手册一本锆

发表于 07-29 16:33

【锆石A4 FPGA试用体验】初识锆石A4 FPGA开发板

` 本帖最后由 jinglixixi 于 2017-8-3 11:14 编辑

期待中的锆石A4 FPGA开发板终于如期而至了,欣喜中快速

发表于 08-03 11:12

【锆石A4 FPGA试用体验】锆石A4智能家庭娱乐系统-结项报告

` 本帖最后由 超级开发板 于 2017-10-8 10:45 编辑

今天,我们来进行基于锆石A4 FPGA

发表于 09-28 08:58

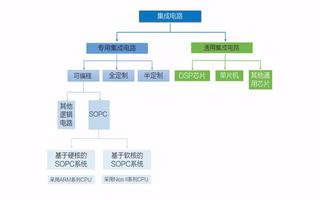

锆石FPGA A4_Nano开发板视频:LED的IP核应用

利用IP核设计电子系统,引用方便,修改基本元件的功能容易。具有复杂功能和商业价值的IP核一般具有知识产权,尽管IP

锆石FPGA A4_Nano开发板视频:内置IP核SystemID的讲解

System ID用来在区域内唯一标识主机或路由器。在设备的实现中,它的长度固定为48bit(6字节)。一般情况下,我们采用设备的router-id转换为System ID。

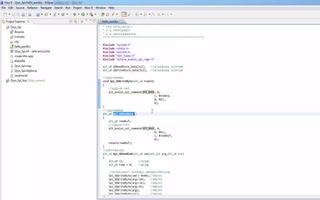

锆石FPGA A4_Nano开发板视频:内置IP核JTAG-UART的讲解

JTAG UART是要自己添加的一个IP核,通常用来是实现PC和Nios II系统间的串行通信接口,它用于字符的输入输出,在Nios II的开发调试过程中扮演了重要的角色。

锆石FPGA A4_Nano开发板视频:什么是Qsys?如何构建一个Qsys系统?

视频中进一步介绍了Nios II处理器的体系结构、Qsys丰富多彩的内置IP,以及Avalon总线接口规范,然后我们又以Avalon总线接口规范为基础,进一步定制了开发板所有外设的

锆石FPGA A4_Nano开发板视频:内置IP核之Interval Timer的应用实战讲解

利用IP核设计电子系统,引用方便,修改基本元件的功能容易。具有复杂功能和商业价值的IP核一般具有知识产权,尽管IP

锆石FPGA A4_Nano开发板视频:内置IP核UART的理论原理讲解

锆石FPGA A4_Nano开发板视频:内置IP核UART的理论原理讲解

评论