软核演练篇包含了哪些内容:该篇以什么是软核、什么是Qsys、如何构建一个Qsys系统为切入点,在该基础上进一步介绍了Nios II处理器的体系结构、Qsys丰富多彩的内置IP,以及Avalon总线接口规范,然后又以Avalon总线接口规范为基础,进一步定制了开发板所有外设的IP核。最后,又以系统uC/OS-II和uCGUI为例进行了应用开发的介绍。本篇不同于传统的傻瓜式教程,将理论和实践相结合,不仅仅讲述了怎样做,更进一步讲述了为什么要这样做。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

处理器

+关注

关注

68文章

19293浏览量

229918 -

FPGA

+关注

关注

1629文章

21744浏览量

603575 -

总线

+关注

关注

10文章

2887浏览量

88112

发布评论请先 登录

相关推荐

【锆石A4 FPGA试用体验】——小炮与锆石A4的故事(7)——软核学习——Qsys入门

相比之前学习数电时对FPGA的学习,经过一段时间对锆石A4的试用之后对FPGA有了一个全新的认识,最近开始学习FPGA深层次的东西,开始学习软核

发表于 10-11 19:28

【锆石A4 FPGA试用体验】Qsys(三)Qsys文件介绍

`由于本人是FPGA的小白,一些基本的东西都要反复的查找,记忆才可以,而对于Qsys应该算是FPGA学习中的重点了。上篇创建了我们自己的Qsys系统

发表于 10-16 10:11

【锆石A4 FPGA试用体验】——小炮与锆石A4的故事(9)——软核学习——Nios II硬件框架结构的深入学习(1)

,近期主要深入学习了Qsys系统的硬件部分和软件部分,首先学习了Nios II的硬件框架结构,收

发表于 10-21 16:47

FPGA的软核、硬核以及固核的概念

, 节约将近90% 的逻辑资源。 软核(Soft IP Core) : 软核在EDA 设计领域指的是综合之前的寄存器传输级(RTL) 模型;具体在F

发表于 09-03 11:03

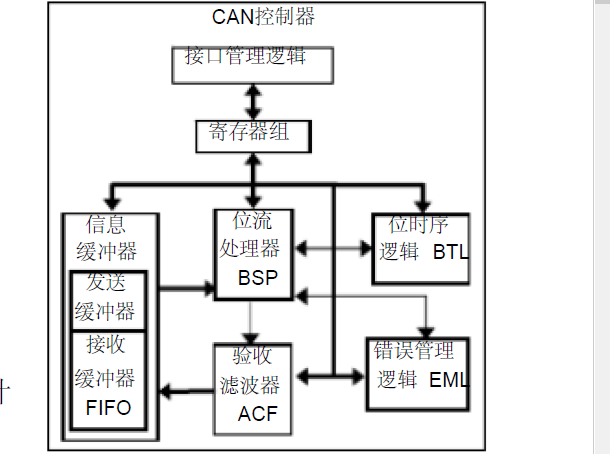

如何使用FPGA进行CAN控制器软核的设计与实现

和Altera 公司部分FPGA 上的资源利用和性能情况。此外,基于SOPC技术将处理器软核和CAN 控制器软

发表于 07-19 17:48

•25次下载

FPGA 系统中的处理器核们(二):软核,可杀鸡亦可屠龙?

在前文中,我们了解到两种 FPGA 嵌入式处理器核方案:软核与硬核。本文将展开讨论软核在一个基于

发表于 02-07 10:07

•3次下载

FPGA之软核演练篇:构建Qsys系统的硬件部分

FPGA之软核演练篇:构建Qsys系统的硬件部分

评论