FIFO队列具有处理简单,开销小的优点。但FIFO不区分报文类型,采用尽力而为的转发模式,使对时间敏感的实时应用(如VoIP)的延迟得不到保证,关键业务的带宽也不能得到保证。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1663文章

22493浏览量

638950 -

带宽

+关注

关注

3文章

1048浏览量

43556 -

fifo

+关注

关注

3文章

407浏览量

45893

发布评论请先 登录

相关推荐

热点推荐

求助verilog编写实现AXIStream-FIFO功能思路

各位大神,有没有用过AXIStream-FIFO IP core的或不用core直接用verilog实现过AXIStream-FIFO功能的,我现在FPGA入门练习(据说华为等大公司喜

发表于 02-21 16:24

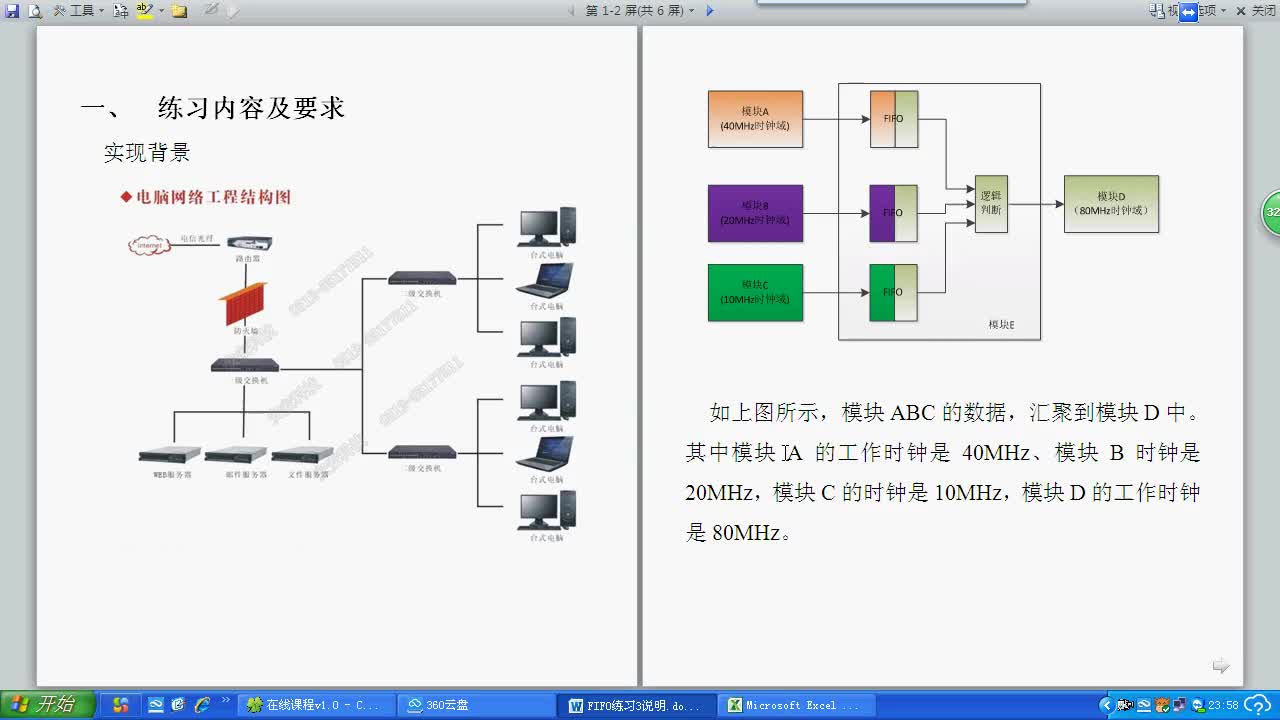

明德扬点拨FPGA在线培训课程下载 很实用的资料

课程就足够学习FPGA,无须再学习其他资料,是您学习FPGA的最佳选择。感觉课程非常实用,与众不同的地方在于,它练习很多,而且会先出一个功能文档,然后按照文档设计,接着对照设计思路,看

发表于 05-20 14:47

Xilinx FPGA入门连载52:FPGA片内FIFO实例之FIFO配置

Xilinx FPGA入门连载52:FPGA片内FIFO实例之FIFO配置特权同学,版权所有配套例程和更多资料下载链接:http://pan

发表于 02-29 13:35

FPGA之FIFO练习

FIFO队列具有处理简单,开销小的优点。但FIFO不区分报文类型,采用尽力而为的转发模式,使对时间敏感的实时应用(如VoIP)的延迟得不到保证,关键业务的带宽也不能得到保证。

FPGA之FIFO练习3:设计思路

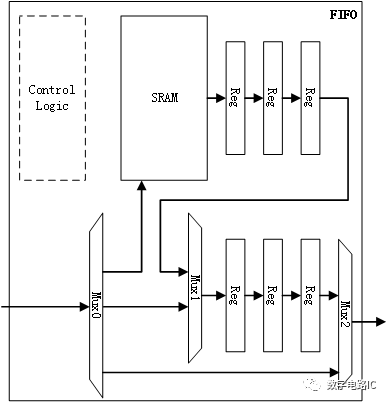

根据FIFO工作的时钟域,可以将FIFO分为同步FIFO和异步FIFO。同步FIFO是指读时钟和写时钟为同一个时钟。在时钟沿来临时同时发生读

FPGA之异步练习1:设计思路

基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统。但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免。

FPGA之FIFO练习2:设计思路

FIFO( First Input First Output)简单说就是指先进先出。由于微电子技术的飞速发展,新一代FIFO芯片容量越来越大,体积越来越小,价格越来越便宜。

FPGA之异步练习:设计思路

在异步设计中,完全避免亚稳态是不可能的。因此,设计的基本思路应该是:首先尽可能减少出现亚稳态的可能性,其次是尽可能减少出现亚稳态并给系统带来危害的可能性。

FPGA学习-基于FIFO的行缓存结构

在FPGA中对图像的一行数据进行缓存时,可以采用FIFO这一结构,如上图所示,新一行图像数据流入到FIFO1中,FIFO1中会对图像数据进行缓存,当

XILINX FPGA IP之FIFO Generator例化仿真

上文XILINX FPGA IP之FIFO对XILINX FIFO Generator IP的特性和内部处理流程进行了简要的说明,本文通过实际例子对该IP的使用进行进一步的说明。本例子

FPGA之FIFO练习1:设计思路

FPGA之FIFO练习1:设计思路

评论