异步时序电路是指电路中除以使用带时钟的触发器外,还可以使用不带时钟的触发器和延迟元件作为存储元件;电路中没有统一的时钟;电路状态的改变由外部输入的变化直接引起。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1631文章

21806浏览量

606722 -

存储

+关注

关注

13文章

4367浏览量

86262 -

触发器

+关注

关注

14文章

2019浏览量

61398

发布评论请先 登录

相关推荐

FPGA实战演练逻辑篇54:VGA驱动接口时序设计之1概述

VGA驱动接口时序设计之1概述本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 第六章第8节中

发表于 07-26 21:56

用FPGA模拟VGA时序PS_2总线的键盘接口VHDL源代码

Xilinx FPGA工程例子源码:用FPGA模拟VGA时序PS_2总线的键盘接口VHDL源代码

发表于 06-07 15:11

•33次下载

FPGA异步练习之测试文件(2)

FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最终决定了FPGA所能实现的功能,FPGA允许无限次的编程。

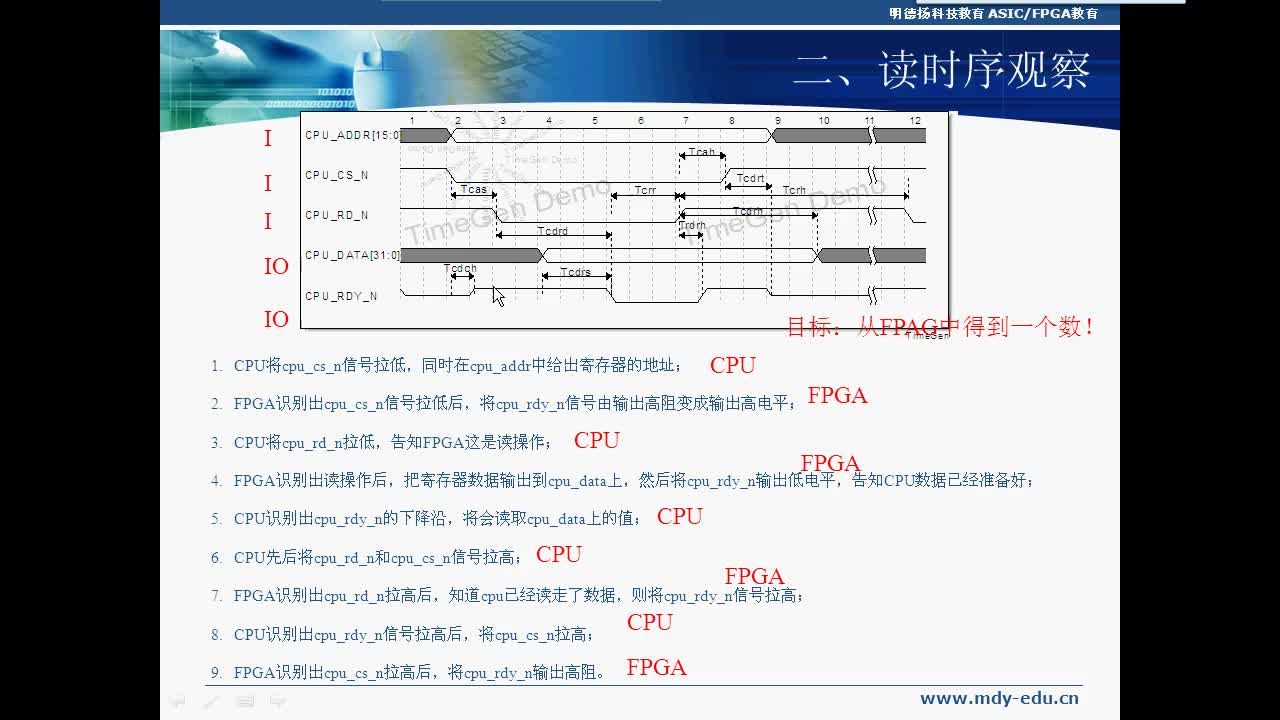

FPGA之异步练习1:设计思路

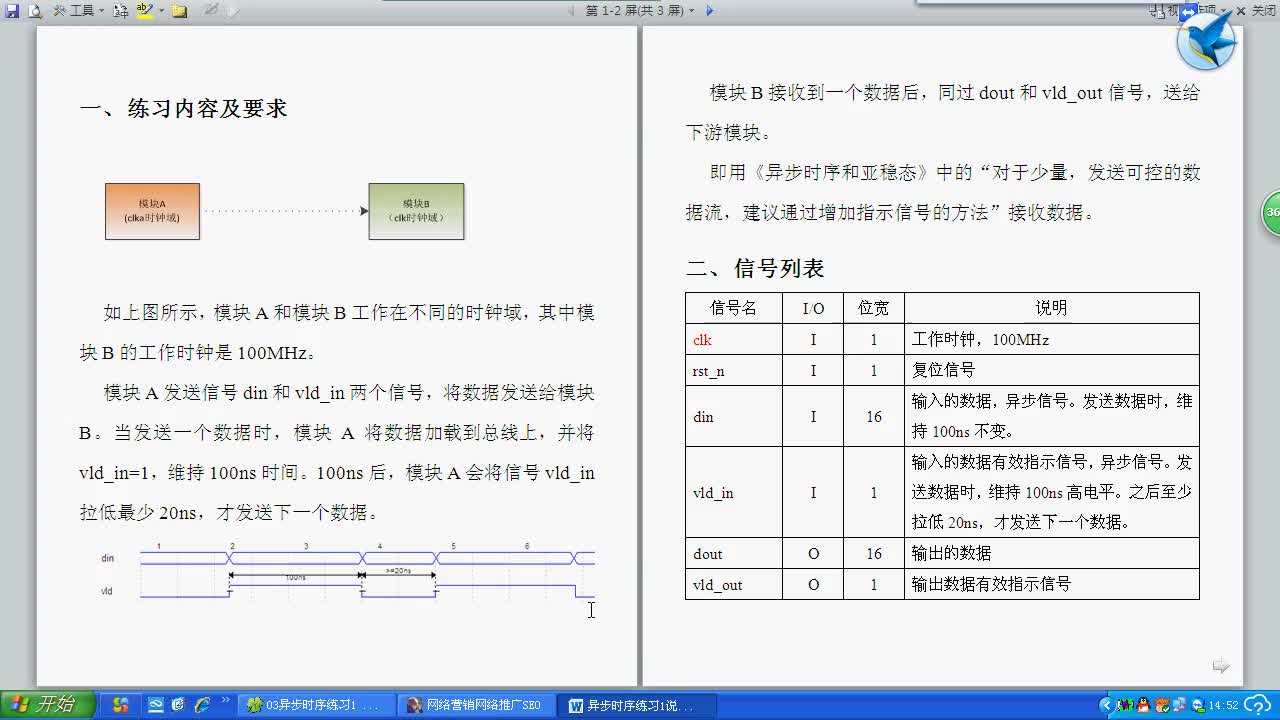

基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统。但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免。

FPGA之何为异步时序

异步时序电路是指电路中除以使用带时钟的触发器外,还可以使用不带时钟的触发器和延迟元件作为存储元件;电路中没有统一的时钟;电路状态的改变由外部输入的变化直接引起.

FPGA之异步练习2:接口时序参数

FPGA之异步练习2:接口时序参数

评论