在计算机中,先入先出队列是一种传统的按序执行方法,先进入的指令先完成并引退,跟着才执行第二条指令(指令就是计算机在响应用户操作的程序代码,对用户而言是透明的)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

计算机

+关注

关注

19文章

7486浏览量

87844 -

仿真

+关注

关注

50文章

4070浏览量

133542 -

fifo

+关注

关注

3文章

387浏览量

43640

发布评论请先 登录

相关推荐

Efinity FIFO IP仿真问题 -v1

Efinity目前不支持联合仿真,只能通过调用源文件仿真。 我们生成一个fifo IP命名为fifo_sim 在Deliverables中保留Testbench的选项。 在IP的生成目

SPICE可以用来验证电路设计以预测电路功能吗?

SPICE虽然最初是用来做IC设计,但是由于低成本运算以及稳定设计的推动,越来越多的电路和系统设计人员已经意识到了模拟电路仿真的优点。但是SPICE可以用来验证电路设计以预测

发表于 04-07 06:34

高速异步FIFO的设计与实现

本文主要研究了用FPGA 芯片内部的EBRSRAM 来实现异步FIFO 设计方案,重点阐述了异步FIFO 的标志信号——空/满状态的设计思路,并且用VHDL 语言实现,最后进行了仿真验证

发表于 01-13 17:11

•40次下载

基于LabVIEW的数字电路设计和仿真

基于LabVIEW的数字电路设计和仿真

数字电路设计和仿真是电子工程领域的基本技术。介绍了基于LabV IEW的数字电路设计和

发表于 03-30 16:09

•124次下载

基于软件仿真验证的运放电路设计方法

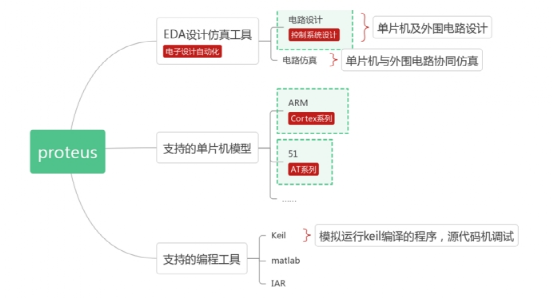

本文探讨了使用仿真软件设计电路的可行性,并给出了典型的电压反馈取样电路设计方法,Proteus 软件是目前能够对微处理器进行较好仿真的软件,真正实现了从概念到产品的设计

发表于 02-17 10:08

•2585次阅读

Multisim电路设计与仿真

设计和后处理功能,还可以进行从原理图到 PCB 布线工具包的无缝隙数 据传输。 对于电路设计者来说,能满足电路电子设计与仿真,满足从参数到产品的 设计要求,节约电路设计时间,降低实验

发表于 05-13 15:07

•27次下载

关于Mentor电路设计仿真验证平台软件的分析和介绍

Mentor电路设计仿真验证平台软件赠予仪式北恩科技总经理杨晔先生发言强调,学校和企业是社会发展生命周期的两个环节,企业为社会提供物质保障,学校为社会发展的提供人才保障,校企合作是产业和社会发展的一

Verilog数字系统设计——复杂数字电路设计2(FIFO控制器设计)

Verilog数字系统设计十二复杂数字电路设计2文章目录Verilog数字系统设计十二前言一、什么是FIFO控制器?二、编程1.要求:2.设计思路:3.FIFO控制器实现:总结前言 随着人工智能

发表于 12-05 15:51

•9次下载

射频PCB电路设计与仿真案例

在进行射频PCB电路设计的时候,我们一般靠“经验”和“原则”指导设计,某些情况经验的作用也是有限的。要设计好射频板级电路,仿真是必不可少的。之所以某些经验可以替代仿真,是因为产品的

数字电路设计有哪些仿真验证流程

数字电路设计的仿真验证流程是确保设计能够正确运行的重要步骤之一。在现代电子设备中,数字电路被广泛应用于各种应用领域,如计算机、通信设备、汽车电子等等。因此,设计师必须通过

FIFO的电路设计与仿真验证

FIFO的电路设计与仿真验证

评论