TimeQuest Timing Analyzer是一个功能强大的,ASIC-style的时序分析工具。采用工业标准--SDC(synopsys design contraints)--的约束、分析和报告方法来验证你的设计是否满足时序设计的要求。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

asic

+关注

关注

34文章

1193浏览量

120303 -

工具

+关注

关注

4文章

307浏览量

27732 -

TimeQuest

+关注

关注

0文章

11浏览量

11362

发布评论请先 登录

相关推荐

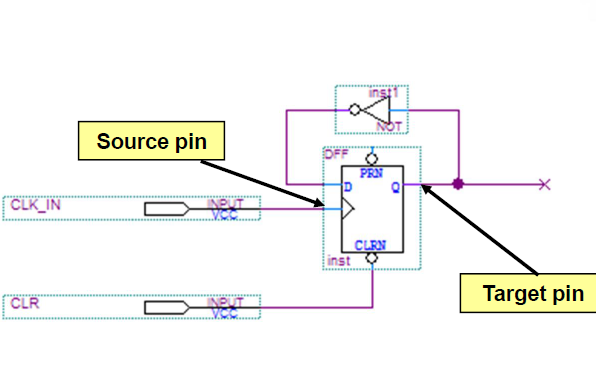

传统时序分析器TAN到基于SDC的Timequest时序分析器转换教程

1.Convert a design from using the Classic timing analyzer to using the TimeQuest timing

发表于 02-03 10:55

基于Astro工具的ASIC时序分析

挑战。本文主要介绍了逻辑设计中值得注意的重要时序问题,以及如何克服这些问题。最后介绍了利用Astro工具进行时序分析的方法。关键词:ASIC;同步数字电路;

发表于 11-09 19:04

ETD第14期:SDR源同步接口时序约束方法

。本次沙龙主要介绍怎样通过Quartus® II软件中的TimeQuest时序分析器来约束并分析单倍数据速率源同步接口。会议焦点 1、源同步接口相对于公共时钟系统接口有何优点? 2

发表于 12-31 14:21

TimeQuest新手入门

笔者常常在思考,虽说TimeQuest是一个分析物理时序是否合格的数学工具,但是TimeQuest真正意义上是在针对什么?这是一个很有趣的问

发表于 08-02 07:35

如何使用TimeQuest

用Altera的话来说,TimeQuest Timing Analyzer是一个功能强大的,ASIC-style的时序分析工具。采用工业标准--SDC(synopsys design

静态时序分析:如何编写有效地时序约束(一)

的活!)。无需用向量(激励)去激活某个路径,分析工具会对所有的时序路径进行错误分析,能处理百万门级的设计,

正点原子FPGA静态时序分析与时序约束教程

静态时序分析是检查芯片时序特性的一种方法,可以用来检查信号在芯片中的传播是否符合时序约束的要求。相比于动态时序

发表于 11-11 08:00

•62次下载

调用timequest工具对工程时序进行分析

调用timequest工具对工程时序进行分析

评论