声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1631文章

21806浏览量

606722 -

可编程逻辑

+关注

关注

7文章

517浏览量

44202 -

quartus

+关注

关注

16文章

171浏览量

74742

发布评论请先 登录

相关推荐

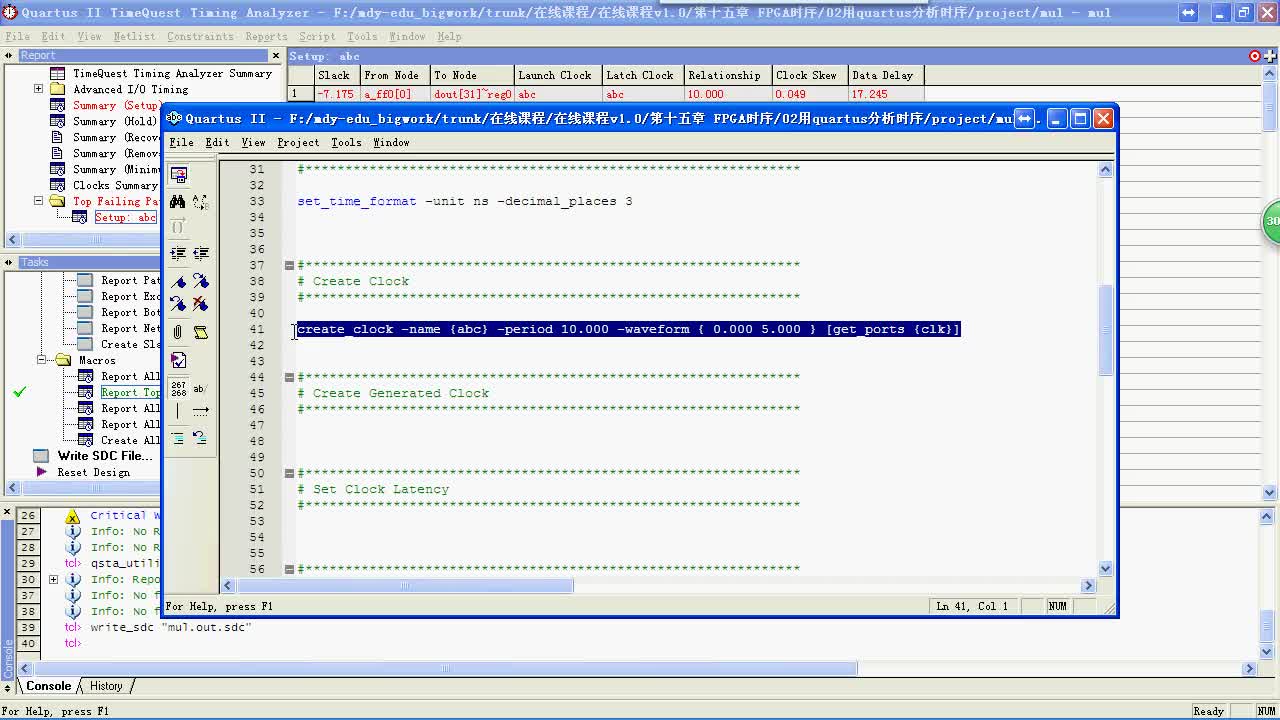

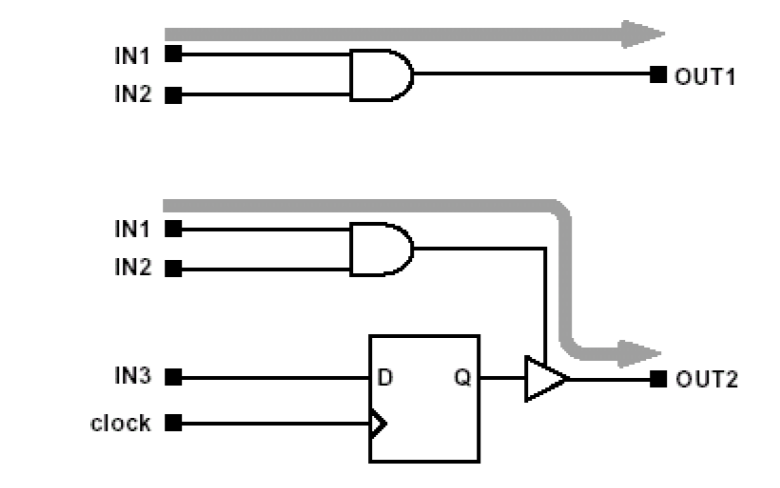

FPGA quartus ii里的静态时序分析

在fpga工程中加入时序约束的目的: 1、给quartusii 提出时序要求; 2、quartusii 在布局布线时会尽量优先去满足给出的时序要求; 3、STA静态

FPGA的IO口时序约束分析

在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,

发表于 09-27 09:56

•1807次阅读

静态时序分析在高速 FPGA设计中的应用

介绍了采用STA (静态时序分析)对FPGA (现场可编程门阵列)设计进行时序验证的基本原理,并介绍了几种与STA相关联的时序约束。针对

发表于 05-27 08:58

•70次下载

正点原子FPGA静态时序分析与时序约束教程

时序分析结果,并根据设计者的修复使设计完全满足时序约束的要求。本章包括以下几个部分: 1.1 静态时序分析简介 1.2

发表于 11-11 08:00

•65次下载

如何读懂FPGA开发过程中的Vivado时序报告?

FPGA开发过程中,vivado和quartus等开发软件都会提供时序报告,以方便开发者判断自己的工程时序是否满足时序要求。

发表于 06-26 15:29

•1175次阅读

FPGA时序:用quartus分析时序

FPGA时序:用quartus分析时序

评论