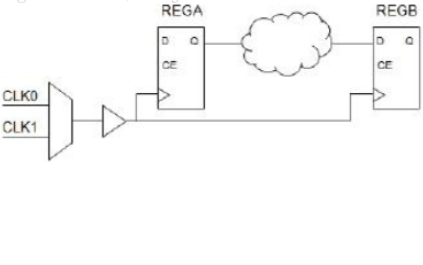

针对普通时钟系统存在着限制时钟频率的弊端,人们设计了一种新的时序系统,称之为源同步时序系统。它最大的优点就是大大提升了总线的速度,在理论上信号的传送可以不受传输延迟的影响。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

时钟

+关注

关注

10文章

1733浏览量

131475 -

总线

+关注

关注

10文章

2881浏览量

88080 -

时序

+关注

关注

5文章

387浏览量

37330

发布评论请先 登录

相关推荐

对边沿对齐源同步输入端口的约束

相对于FPGA来说,边沿对齐源同步输入端口,指的是FPGA同时接收外部器件传过来的数据和时钟信号,并且用接收到的时钟信号去锁存传过来的数据。模型如下图所示:对此模型进行约束,分下面几个步骤

发表于 12-25 14:28

ETD第14期:SDR源同步接口时序约束方法

。本次沙龙主要介绍怎样通过Quartus® II软件中的TimeQuest时序分析器来约束并分析单倍数据速率源同步接口。会议焦点 1、源

发表于 12-31 14:21

FPGA沙龙:SDR源同步接口时序约束方法沙龙精彩内容回顾!

草丛中两只花,今天的沙龙现场我们还迎来了两位美女工程师,有木有感觉本次沙龙的氛围更加轻松了呢~~~!张工正在为大家介绍SDR源同步接口时序约束,学会这个保证你贯穿全部

发表于 12-31 14:25

FPGA实战演练逻辑篇55:VGA驱动接口时序设计之2源同步接口

可以分析一下这个接口的时序要求,然后对其进行约束。这个输出的信号,其实是很典型的源同步接口,它的时钟和数据都是由FPGA来驱动产生的。一般的源

发表于 07-29 11:19

基于Cadence的源同步时序仿真

根据源同步的一些基本问题,在Cadence仿真环境下,对源同步时序进行仿真,仿真结果表明,设计能满足噪声容限和过冲,仿真后的可知数据线和时间

发表于 05-29 15:26

•0次下载

FPGA时序约束的常用指令与流程详细说明

说到FPGA时序约束的流程,不同的公司可能有些不一样。反正条条大路通罗马,找到一种适合自己的就行了。从系统上来看,同步时序

发表于 01-11 17:46

•13次下载

时序约束步骤:系统同步与源同步

时序约束步骤:系统同步与源同步

评论