Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。被建模的数字系统对象的复杂性可以介于简单的门和完整的电子数字系统之间。数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。

Verilog HDL 语言具有下述描述能力:设计的行为特性、设计的数据流特性、设计的结构组成以及包含响应监控和设计验证方面的时延和波形产生机制。所有这些都使用同一种建模语言。此外,Verilog HDL语言提供了编程语言接口,通过该接口可以在模拟、验证期间从设计外部访问设计,包括模拟的具体控制和运行。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

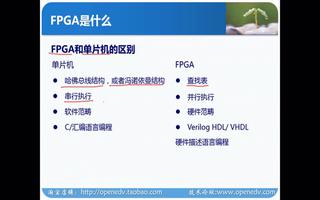

FPGA

+关注

关注

1664文章

22502浏览量

639214 -

Verilog

+关注

关注

31文章

1374浏览量

114720

发布评论请先 登录

相关推荐

热点推荐

【正点原子FPGA连载】第十二章 动态数码管显示实验

`1)实验平台:正点原子开拓者FPGA开发板2)平台购买地址:https://item.taobao.com/item.htm?id=5797492098202)全套实验源码+手册+

发表于 06-15 22:54

分享正点原子FPGA开发板全套资料

本帖最后由 100dongdong 于 2020-5-16 23:48 编辑

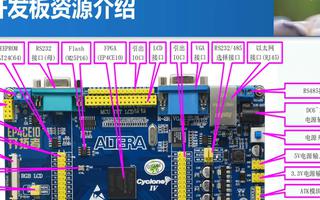

正点原子FPGA开拓者开发板,Intel(Altera) FPG

发表于 05-16 23:35

正点开拓者FPGA开发板使用问题

求问各位大佬,刚刚入门正点开拓者FPGA开发板,用板载pcf8591采集信号发生器单一频率正弦波,再用ip核做fft,结果和matlab上fft不一样,请问是怎么回事呢?

发表于 01-04 09:34

正点原子开拓者FPGA视频:Modelsim软件的使用

Mentor公司的ModelSim是业界最优秀的HDL语言仿真软件,它能提供友好的仿真环境,是业界唯一的单内核支持VHDL和Verilog混合仿真的仿真器。它采用直接优化的编译技术、Tcl/Tk技术

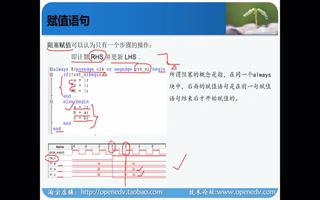

正点原子开拓者FPGA视频:Verilog高级知识点

Verilog HDL语言不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。因此,用这种语言编写的模型能够使用Verilog仿真器进行验证。语言从C编程语言中继承了多种操

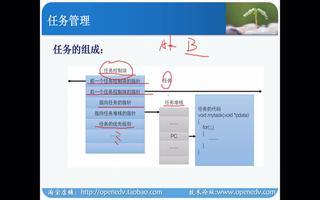

正点原子开拓者FPGA Qsys视频:uCOS II任务管理与时间管理(2)

该课程是正点原子团队编写,详细讲解了quartus中的qsys。也可以从我头像点进去看FPGA verilog相关的视频。

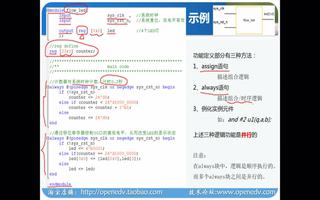

正点原子开拓者FPGA:Verilog程序框架

Verilog HDL 语言具有下述描述能力:设计的行为特性、设计的数据流特性、设计的结构组成以及包含响应监控和设计验证方面的时延和波形产生机制。所有这些都使用同一种建模语言。此外,Verilog

正点原子开拓者FPGA视频:Verilog基础语法

正点原子开拓者FPGA视频:Verilog基础语法

评论