计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS触发器、T触发器、D触发器及JK触发器等。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1629文章

21736浏览量

603329 -

计数器

+关注

关注

32文章

2256浏览量

94563 -

触发器

+关注

关注

14文章

2000浏览量

61153

发布评论请先 登录

相关推荐

FPGA学习合集教程之开发板数据手册和三个仿真测试的视频教程

本文档的主要内容详细介绍的是FPGA学习合集教程之开发板数据手册和三个仿真测试的视频教程内容包括了:CPLD EPM240 EVB开发

发表于 12-27 08:00

•29次下载

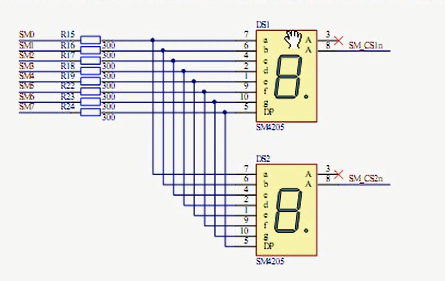

FPGA视频教程之使用BJ-EPM240学习板进行数码管显示实验的资料说明

本文档的主要内容详细介绍的是FPGA视频教程之使用BJ-EPM240学习板进行数码管显示实验的资

发表于 02-28 10:35

•5次下载

FPGA视频教程之BJ-EPM240学习板的详细资料介绍

本文档的主要内容详细介绍的是FPGA视频教程之BJ-EPM240学习板的详细资料说明免费下载,BJ-EP

发表于 03-01 11:35

•20次下载

FPGA视频教程之BJ-EPM240学习板实验之分频计数实验的资料说明

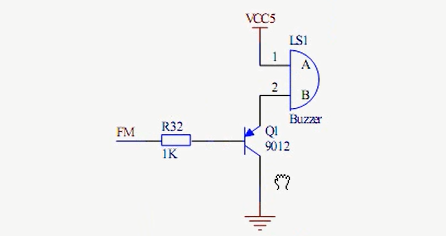

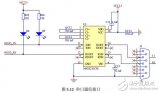

这个实验可以说是verilog入门最基础的实验了,我们不做太多的理论分析,实践是硬道理。蜂鸣器与CPLD的接口如图5.2所示,当CPLD的1/0口(FM) 为低电平时,三极管截至,蜂鸣器不发声;当CPLD的I/0 (FM)为高电平时,三极管导通,蜂鸣器发声。

发表于 03-01 16:13

•2次下载

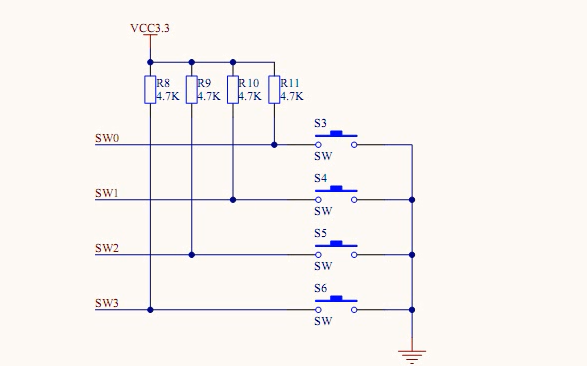

FPGA视频教程之BJ-EPM240学习板Johnson计数器实验的详细资料说明

所谓Johnson计数器,其实说白了无非就是复杂一-点的流水灯实验。流水灯加上了按键控制,流水灯的开启关闭和变化方向在按键的控制下进行。本实例是带停止控制的双向4bit Johnson 计数器,可以通过LED灯直观的在

发表于 03-04 17:06

•6次下载

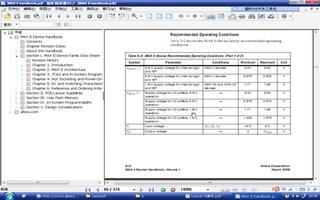

BJ-EPM240学习板介绍

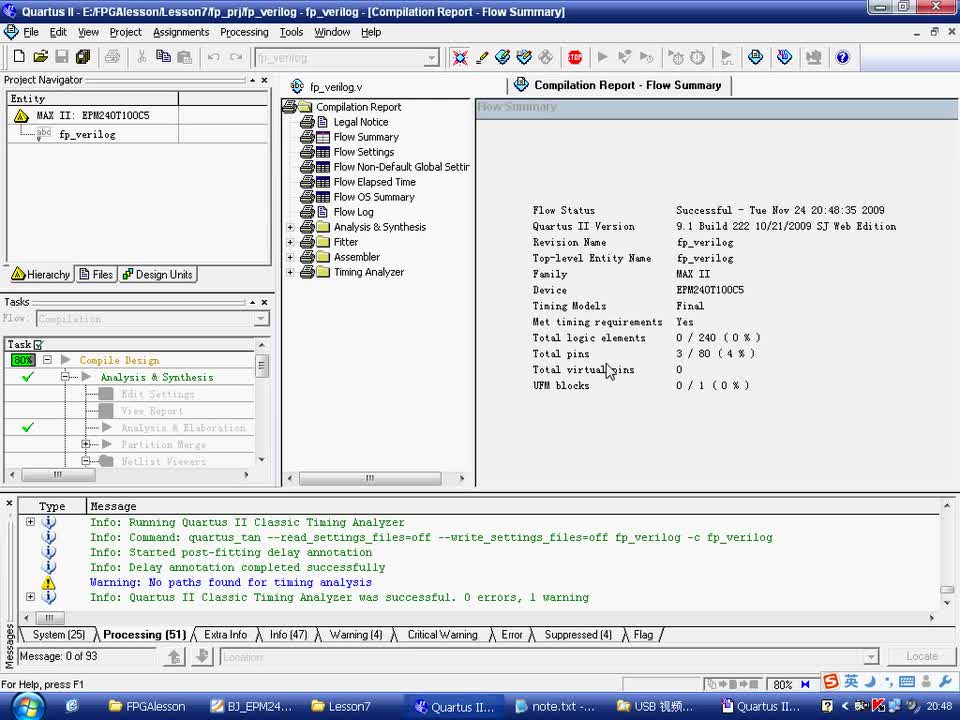

主芯片使用的是Altera公司的MAXII系列EPM240T100C5,该芯片有240个逻辑单元,等效宏单元192个,资源比较丰富,内有8KbitFlash的存储空间。

BJ-EPM240学习板之分频计数实验

这个实验可以说是verilog入门最基础的实验了,我们不做太多的理论分析,实践是硬道理。蜂鸣器与CPLD的接口如图所示,当CPLD的1/0口(FM) 为低电平时,三极管截至,蜂鸣器不发声;当CPLD的I/0 (FM)为高电平时,三极管导通,蜂鸣器发声。

FPGA视频教程:BJ-EPM240学习板-分频计数实验

FPGA视频教程:BJ-EPM240学习板-分频计数实验

评论