声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1629文章

21729浏览量

602978 -

时钟

+关注

关注

10文章

1733浏览量

131446 -

状态机

+关注

关注

2文章

492浏览量

27528

发布评论请先 登录

相关推荐

FPGA工程师:如何在FPGA中实现状态机?

安全高效的状态机设计对于任何使用FPGA的工程师而言都是一项重要技能。选择Moore状态机、Mealy状态机还是混合机取决于整个系统的需求。

发表于 03-29 15:02

•1.3w次阅读

数字设计FPGA应用:时钟同步状态机及其设计流程

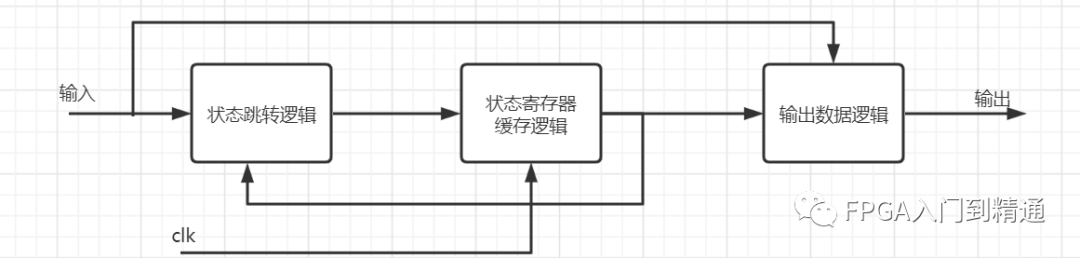

状态机可归纳为4个要素,即现态、条件、动作、次态。这样的归纳,主要是出于对状态机的内在因果关系的考虑。“现态”和“条件”是因,“动作”和“次态”是果。

数字设计FPGA应用:时钟同步状态机设计方法构建序列发生器

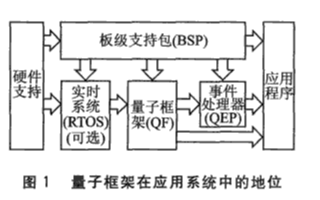

状态机由状态寄存器和组合逻辑电路构成,能够根据控制信号按照预先设定的状态进行状态转移,是协调相关信号动作,完成特定操作的控制中心。状态机分为

如何在FPGA中实现状态机

状态机往往是FPGA 开发的主力。选择合适的架构和实现方法将确保您获得一款最佳解决方案。 FPGA 常常用于执行基于序列和控制的行动, 比如实现一个简单的通信协议。对于设计人员来说,满足这些行动

基于FPGA的状态机设计

状态机的基础知识依然强烈推荐mooc上华科的数字电路与逻辑设计,yyds!但是数电基础一定要和实际应用结合起来,理论才能发挥真正的价值。我们知道FPGA是并行执行的,如果我们想要处理具有前后顺序的事件就需要引入

如何在FPGA中实现状态机

在FPGA(现场可编程门阵列)中实现状态机是一种常见的做法,用于控制复杂的数字系统行为。状态机能够根据当前的输入和系统状态,决定下一步的动作

数字设计FPGA应用:时钟同步状态机的设计

数字设计FPGA应用:时钟同步状态机的设计

评论