- Load:0 second

- Duration:0 second

- Size:0x0

- Volume:0%

- Fps:60fps

- Sudio decoded:0 Byte

- Video decoded:0 Byte

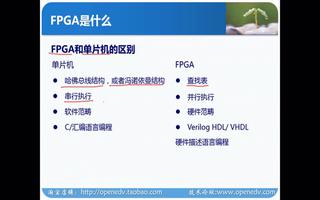

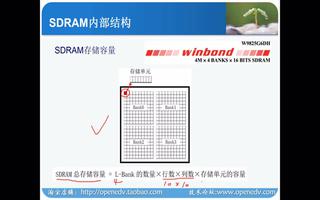

同步动态随机存取内存(synchronous dynamic random-access memory,简称SDRAM)是有一个同步接口的动态随机存取内存(DRAM)。通常DRAM是有一个异步接口的,这样它可以随时响应控制输入的变化。而SDRAM有一个同步接口,在响应控制输入前会等待一个时钟信号,这样就能和计算机的系统总线同步。时钟被用来驱动一个有限状态机,对进入的指令进行管线(Pipeline)操作。这使得SDRAM与没有同步接口的异步DRAM(asynchronous DRAM)相比,可以有一个更复杂的操作模式。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1631文章

21807浏览量

606767 -

SDRAM

+关注

关注

7文章

433浏览量

55418 -

内存

+关注

关注

8文章

3071浏览量

74422

发布评论请先 登录

相关推荐

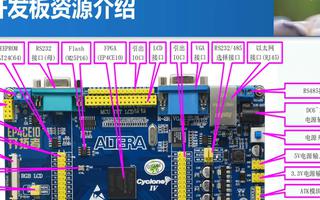

分享正点原子FPGA开发板全套资料

本帖最后由 100dongdong 于 2020-5-16 23:48 编辑

正点原子FPGA开拓者开发板,Intel(Altera) FPG

发表于 05-16 23:35

正点开拓者FPGA开发板使用问题

求问各位大佬,刚刚入门正点开拓者FPGA开发板,用板载pcf8591采集信号发生器单一频率正弦波,再用ip核做fft,结果和matlab上fft不一样,请问是怎么回事呢?

发表于 01-04 09:34

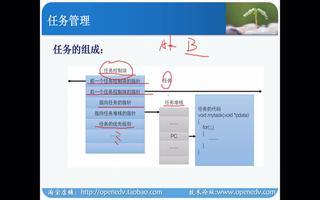

正点原子开拓者FPGA Qsys视频:uCOS II任务管理与时间管理(2)

该课程是正点原子团队编写,详细讲解了quartus中的qsys。也可以从我头像点进去看FPGA verilog相关的视频。

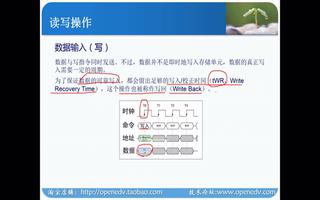

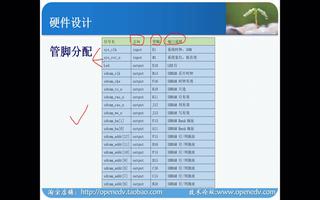

正点原子开拓者FPGA:SDRAM时序操作(2)

通常DRAM是有一个异步接口的,这样它可以随时响应控制输入的变化。而SDRAM有一个同步接口,在响应控制输入前会等待一个时钟信号,这样就能和计算机的系统总线同步。

正点原子开拓者FPGA:SDRAM读写测试实验

SDRAM在计算机中被广泛使用,从起初的SDRAM到之后一代的DDR(或称DDR1),然后是DDR2和DDR3进入大众市场,2015年开始DDR4进入消费市场。

正点原子开拓者FPGA:SDRAM时序操作

正点原子开拓者FPGA:SDRAM时序操作

评论