Verdi的智能加载技术(通过VCS Unified Compile实现)带来快五倍的设计加载和追踪速度

VC验证IP通过VCS统一约束求解器技术实现高两倍的仿真性能

VC Formal测试平台分析器应用和Certitude的原生集成实现快10倍的测试平台质量评估和断言

全新VC加速验证IP,加上VCS和ZeBu的原生集成,可将仿真性能提高10至100倍

新思科技近日发布新版Verification Continuum™平台,将各种验证工具进行新的原生集成,实现高达五倍的验证性能。Verification Continuum平台基于新思科技开发的高速引擎,包括Virtualizer™虚拟原型、SpyGlass®静态验证、VC Formal®形式验证、VCS®软件仿真、ZeBu®硬件加速仿真、HAPS®原型、Verdi®调试和VC验证IP (VIP)。日益增加的片上系统(SoC)复杂性和软件内容以及上市时间压力对高效验证平台的需求更加紧迫。Verification Continuum的全新增强型原生集成实现了所有验证引擎之间的性能提升,加快了复杂片上系统设计的上市。

“Innovium高度创新的生产就绪型TERALYNX™数据中心以太网交换机芯片可实现2T b/s至12.8T b/s的速度。为实现我们的远大目标,依托新思科技VCS的业界领先性能以及用于以太网和源代码测试套件的VC验证IP来加快我们市场领先的交换机产品的流片计划。”

——Avinash Mani

Innovium工程设计副总裁

“为了获得竞争优势,我们需要全方位解决方案来改善验证流程,并缩短高性能人工智能(AI)解决方案的上市时间。新思科技VC Formal控制和数据路径应用,加上VCS的原生编译和Verdi的统一调试,使我们能够在数分钟内发现无用代码,并在一天内检验复杂的128 x 128 MAC。”

——梁斌

天数智芯(Iluvatar)市场副总裁

新的原生集成

• 仿真和调试——新版Verdi提供通过VCS Unified Compile实现的智能加载技术,将Verdi设计加载速度提高五倍。此外,增强型原生多线程将文件写出带来的资源消耗降低50%;新的动态波形混叠技术使得FSDB文件大小缩小三倍。

• 静态验证、动态仿真和调试——SpyGlass和VCS Unified Compile的原生集成可实现DesignWare® IP和加密IP设计的无缝读入,较之前的IP黑盒显著改善了易用性。此外,Verdi的Unified Debug接口与SpyGlass的集成使得整个验证流程在调试过程中提供一致的用户体验。

• 形式化验证和功能验证——新版VC Formal可通过增强型引擎优化和组合将性能提高两倍。VC Formal测试平台分析器应用和Certitude®功能验证系统的原生集成可实现快10倍的测试平台质量评估和断言。这可以通过一个智能故障注入(形式化属性验证)实现。

• 软件仿真和验证IP——VCS和VC验证IP的原生集成可使仿真性能速度提高两倍。这可以通过利用原生UVM技术和业界领先的约束求解器技术进行VCS和VC VIP之间的优化来实现。

• 加速VIP、软件仿真和硬件加速仿真——设计和测试平台的统一编译以及支持信号级和事务级通信无缝混合的低延迟接口,加上VCS、ZeBu和加速VIP的原生集成,使得仿真速度较以前只有仿真的时候提高10至100倍。

“新思科技Verification Continuum平台基于业界领先的软硬件验证工具,提供新的原生集成,让设计人员能够加速验证收敛。自推出该平台以来,新思科技在验证研发的大量投入兑现了我们致力于帮助用户缩短先进片上系统设计上市时间的承诺。”

——Ajay Singh

新思科技芯片验证事业部

高级工程副总裁

-

处理器

+关注

关注

68文章

19257浏览量

229630 -

芯片

+关注

关注

455文章

50711浏览量

423074 -

新思科技

+关注

关注

5文章

796浏览量

50334 -

开发平台

+关注

关注

0文章

94浏览量

14275

原文标题:验证性能5倍升级!新思科技升级Verification Continuum平台继续引领技术

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

戴尔升级非结构化存储与数据管理,AI创新引领新变革

新思科技7月份行业事件

IR600怎样从c.inhand.com.cn平台迁移c.inhandcloud.com平台

DM平台管理设备如何进行固件升级?

新思科技引领EMIB封装技术革新,推出量产级多裸晶芯片设计参考流程

ESP32 ota升级固件,为什么提示wifi CA证书不对,后续代码logo不打印?

NVIDIA三大平台引领AI机器人新时代

高通推出两款全新先进音频平台

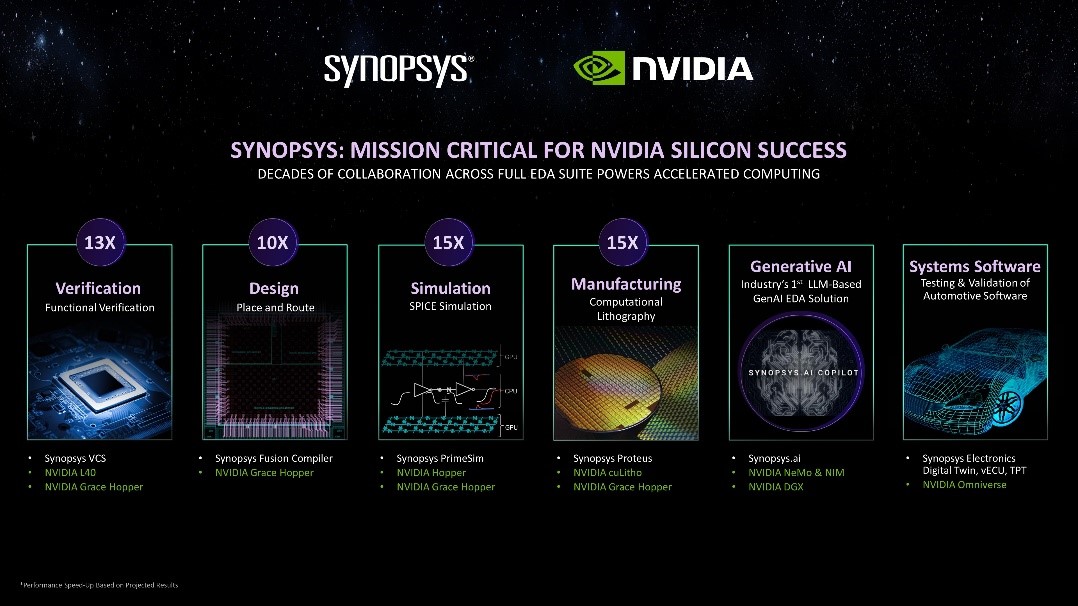

新思科技携手英伟达,全新AI解决方案引领万物智能时代

新思科技携手英伟达:基于加速计算、生成式AI和Omniverse释放下一代EDA潜能

工业智能机器人以其卓越的技术和创新能力,正引领着行业的升级与变革

ZR机械手:创新引领,助力工业自动化升级

新思科技收购Ansys,引领芯片系统设计解决方案

3C电子制造:智慧物流引领产业升级

新思科技升级Verification Continuum平台继续引领技术

新思科技升级Verification Continuum平台继续引领技术

评论