采用CPLD市场领先供应商提供的MAX®II 开发套件,您可以评估MAX II CPLD的系列特性,或者开始对自己的设计进行原型开发。它包括参考设计(LCD控制器、PCI、USB和插槽)、演示设计、软件、电缆以及确保快速方便的使用MAX II CPLD的所有附件。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

cpld

+关注

关注

32文章

1248浏览量

169330 -

控制器

+关注

关注

112文章

16321浏览量

177794 -

lcd

+关注

关注

34文章

4424浏览量

167392

发布评论请先 登录

相关推荐

#硬声创作季 #FPGA 玩转FPGA-18 BJ-EPM240实验11-MAX II内部震荡时钟使用实例-1

fpga时钟发生器EPM实例epM240

水管工

发布于 :2022年10月29日 12:32:53

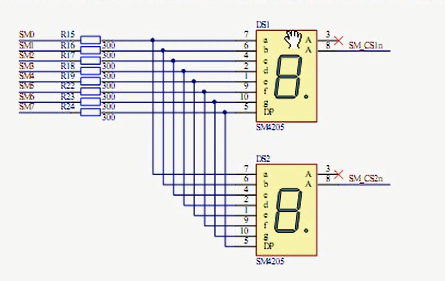

FPGA视频教程之使用BJ-EPM240学习板进行数码管显示实验的资料说明

本文档的主要内容详细介绍的是FPGA视频教程之使用BJ-EPM240学习板进行数码管显示实验的资料说明

发表于 02-28 10:35

•5次下载

FPGA视频教程之BJ-EPM240学习板的详细资料介绍

本文档的主要内容详细介绍的是FPGA视频教程之BJ-EPM240学习板的详细资料说明免费下载,BJ-EPM240学习

发表于 03-01 11:35

•20次下载

BJ-EPM240学习板介绍

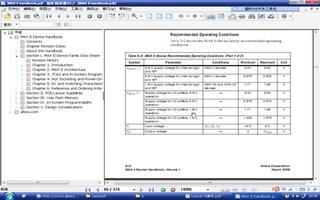

主芯片使用的是Altera公司的MAXII系列EPM240T100C5,该芯片有240个逻辑单元,等效宏单元192个,资源比较丰富,内有8KbitFlash的存储空间。

BJ-EPM240学习板之分频计数实验

这个实验可以说是verilog入门最基础的实验了,我们不做太多的理论分析,实践是硬道理。蜂鸣器与CPLD的接口如图所示,当CPLD的1/0口(FM) 为低电平时,三极管截至,蜂鸣器不发声;当CPLD的I/0 (FM)为高电平时,三极管导通,蜂鸣器发声。

FPGA视频教程:BJ-EPM240学习板-MAX II内部震动时钟使用实验

Altera的MAX® II 系列在所有CPLD系列中,其单位I/O引脚的功耗和成本都是最低的。MAX II CPLD支持高级功能集成,以降低系统设计成本。

FPGA视频教程:BJ-EPM240学习板-MAX II的UFM模块使用实验

MAX II 器件属于非易失、瞬时接通可编程逻辑系列,采用了业界突破性的 CPLD 体系结构。这种体系结构帮助您大大降低了系统功耗、体积和成本。

BJ-EPM240学习板:MAX II内部震动时钟使用实验

BJ-EPM240学习板:MAX II内部震动时钟使用实验

评论