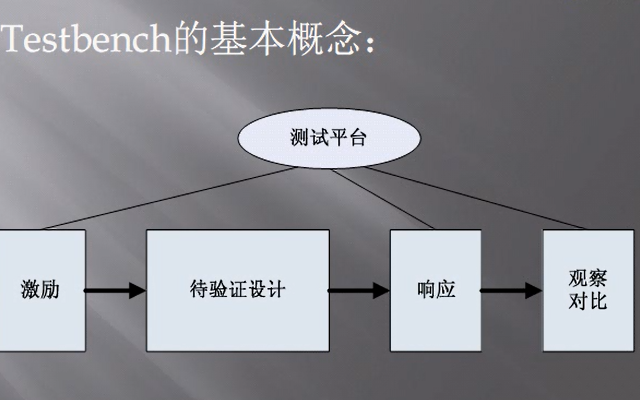

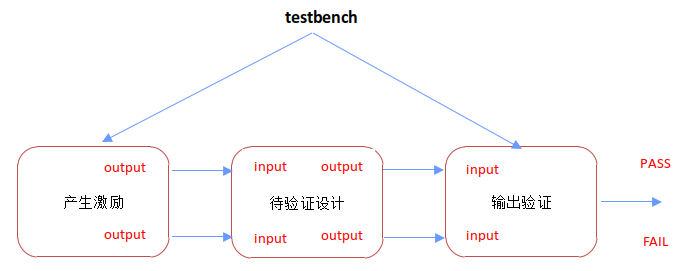

描述测试信号的变化和测试过程的模块叫做测试平台(Testbench),它可以对电路模块进行动态的测试。通过观测被测试模块的输出信号是否符合要求,可以调试和验证逻辑系统的设计和结构是否正确,便于发现问题并修改。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1629文章

21748浏览量

603978 -

测试

+关注

关注

8文章

5318浏览量

126728 -

调试

+关注

关注

7文章

580浏览量

33967

发布评论请先 登录

相关推荐

testbench设置的问题

本帖最后由 平漂流 于 2017-5-21 11:09 编辑

如图,看Verilog仿真视频教程里面,在testbench设置时候,直接复制“blocking_vlg_tst”到top

发表于 05-21 11:04

LFSR testbench V1.2

LFSR testbench

The LFSR testbench can help you understand the LFSR basics:

1. Change

发表于 05-14 11:18

•50次下载

Writing Testbench

Writing Testbench:The Quebec Bridge Company was formed in 1887 and for the nextthirteen years, very

发表于 07-10 17:30

•0次下载

testbench怎么写_testbench经典教程VHDL

testbench是一种验证的手段。首先,任何设计都是会有输入输出的。但是在软环境中没有激励输入,也不会对你设计的输出正确性进行评估。那么此时便有一种,模拟实际环境的输入激励和输出校验的一种“虚拟

发表于 12-01 17:22

•5.6w次阅读

简单的Testbench设计

testbench是一种验证的手段。首先,任何设计都是会有输入输出的。但是在软环境中没有激励输入,也不会对你设计的输出正确性进行评估。那么此时便有一种,模拟实际环境的输入激励和输出校验的一种“虚拟

FPGA视频教程:简单的Testbench设计

testbench是一种验证的手段。首先,任何设计都是会有输入输出的。但是在软环境中没有激励输入,也不会对你设计的输出正确性进行评估。那么此时便有一种,模拟实际环境的输入激励和输出校验的一种“虚拟平台”的产生。在这个平台上你可以对你的设计从软件层面上进行分析和校验。

典型的UVM Testbench架构

UVM类库提供了通用的代码功能,如component hierarchy、transaction level model(TLM),configuration database等等,使用户能够创建任何类型的Testbench架构。

Testbench的基本组成和设计规则

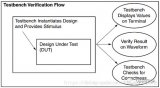

对于小型设计来说,最好的测试方式便是使用TestBench和HDL仿真器来验证其正确性。一般TestBench需要包含这些部分:实例化待测试设计、使用测试向量激励设计、将结果输出到终端或波形窗口便于可视化观察、比较实际结果和预期结果。

编写高效Testbench的指南和示例

Testbench是验证HDL设计的主要手段,本文提供了布局和构建高效Testbench的指南以及示例。另外,本文还提供了一种示例,可以为任何设计开发自检Testbench。

课程8:简单的Testbench设计

课程8:简单的Testbench设计

评论