声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

寄存器

+关注

关注

31文章

5620浏览量

130423 -

时钟

+关注

关注

11文章

1999浏览量

135238 -

时序

+关注

关注

5文章

411浏览量

39005

发布评论请先 登录

相关推荐

热点推荐

FPGA 高级设计:时序分析和收敛

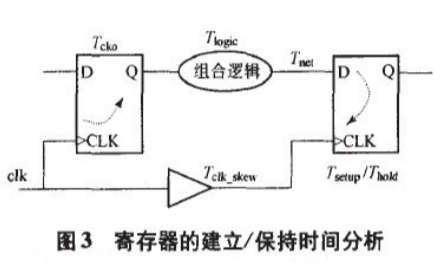

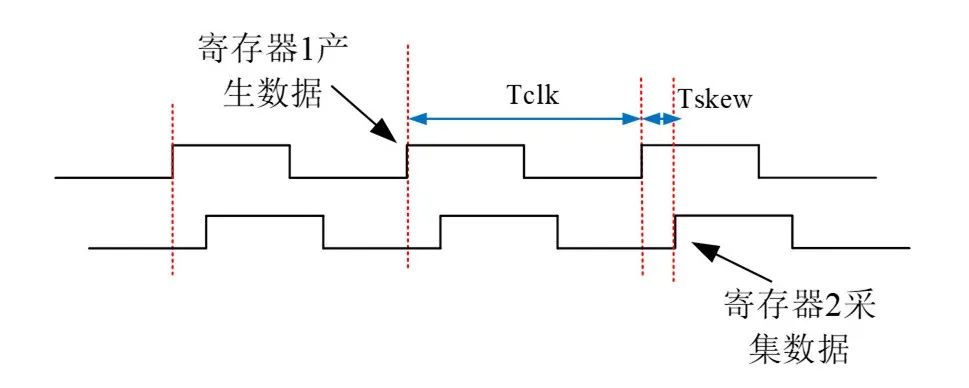

设计都首先要进行周期约束,这样做的好处除了在综合与 布局布线时给出规定目标外,还能让时序分析工具考察整个设计的 Fmax 等。

Altera 的周期定义如图 6 所示,公式描述如下:

图 6

发表于 06-17 17:07

通向FPGA之路---七天玩转Altera教程

本系列教程的宗旨是在力求全面介绍Altera及其QuartusII软件原理的基础上,对何如使用Altera FPGA进行基础设计、时序分析、验证、优化四大方面进行

发表于 12-04 14:36

altera时序约束与分析

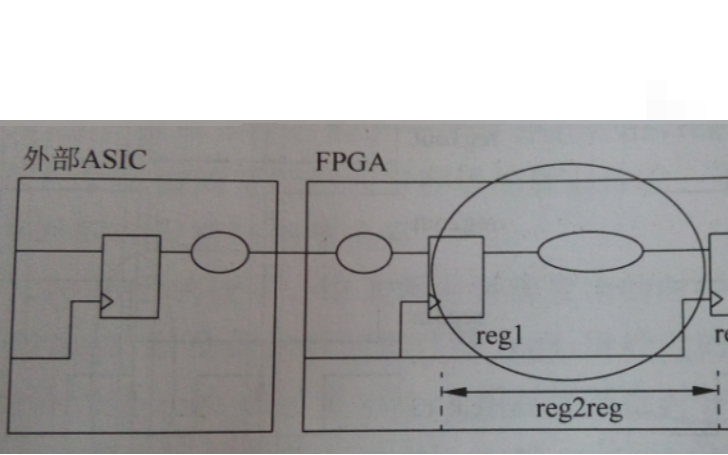

时序分析的主要对象是:在REG2中,时钟信号CLK经过路径③的有效沿,与从REG1寄存器输出的数据经过路径①到达REG2的D端时的关系。

正点原子FPGA静态时序分析与时序约束教程

静态时序分析是检查芯片时序特性的一种方法,可以用来检查信号在芯片中的传播是否符合时序约束的要求。相比于动态时序

发表于 11-11 08:00

•68次下载

ALTERA系列的FPGA时序分析

其中前三类路径是和内部寄存器reg和时钟CLK有关的,因此还需关注内部数据信号与时钟锁存沿的建立时间和保存时间(具体见时序分析一),而最后一类信号的传输通常不经过时钟,因此它的约束也相对简单

发表于 01-08 16:47

•13次下载

FPGA的静态时序分析详细讲解分析

任何学FPGA的人都跑不掉的一个问题就是进行静态时序分析。静态时序分析的公式,老实说很晦涩,而且总能看到不同的版本,内容又不那么一致,为了彻底解决这个问题,我研究了一天,终于找到了一种

发表于 01-12 17:48

•19次下载

RGB时序灯条的工作原理讲解

图文配合讲解了RGB时序灯条的应用场景、什么是RGB时序灯条、信号格式与传输规则、灯珠芯片的工作流程、颜色与动态效果控制方式等

发表于 02-06 11:36

•0次下载

altera时序分析基础项目讲解

altera时序分析基础项目讲解

评论