- Load:0 second

- Duration:0 second

- Size:0x0

- Volume:0%

- Fps:45fps

- Sudio decoded:0 Byte

- Video decoded:0 Byte

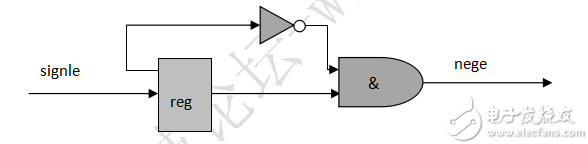

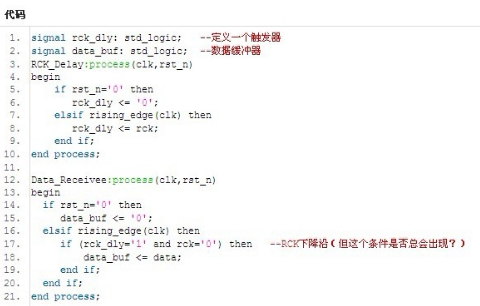

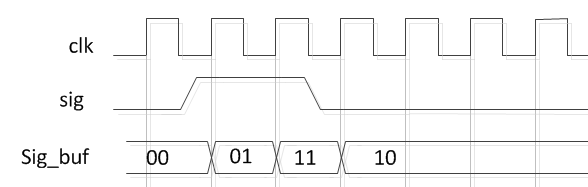

边沿检测电路(edge detection circuit)是个常用的基本电路。所谓边沿检测就是对前一个clock状态和目前clock状态的比较,如果是由0变为1,能够检测到上升沿,则称为上升沿检测电路(posedge edge detection circuit),若是由1变为0,能够检测到下降沿,则被称为下降沿检测电路(negedge edge dttection circuit),能够同时检测上升沿与下降沿的电路称为双沿检测电路(double edge detection)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

检测电路

+关注

关注

13文章

308浏览量

58320 -

边沿检测

+关注

关注

0文章

5浏览量

7853

发布评论请先 登录

相关推荐

FPGA设计中的边沿检测问题

在同步电路设计中,边沿检测是必不可少的!后一种方法所耗的资源要比前一种方法多(一个触发器),但是就可以大大提高可靠性,这绝对是物有所值!!

发表于 02-01 10:53

•993次阅读

关于FPGA进行外部边沿检测,检测不准确问题?

程序边沿检测下降沿并统计数量(数量到达2后重新计数,并发送动作信号),但是最终发现检测结果不准确,有时候能检测到,有时候检测不到。万分感谢您

发表于 08-21 12:58

用移位寄存器实现边沿检测的技巧

本文记录一下关于用移位寄存器实现边沿检测的技巧。要学会硬件思维式的“模块式”读写代码,那么请多看别人的代码,并用ISE或者VIVADO综合出来看看。 边沿检测

发表于 04-15 10:26

•3362次阅读

FPGA学习系列:12. 边沿检测设计

设计背景: 在我们工程设计中,有时会需要到上升沿和下降沿这么一个说法,通过上升沿和下降沿来驱动一个电路,那么学习边沿检测就非常的重要了。 设计原理 : 在学习边沿

Verilog系统函数和边沿检测

“ 本文主要分享了在Verilog设计过程中一些经验与知识点,主要包括Verilog仿真时常用的系统任务、双向端口的使用(inout)、边沿检测”

边沿检测的目的及电路原理分析

边沿检测的目的及电路原理分析

评论