UFM产品是一种在线部署于局域网与广域网之间的All-in-One式的多功能高性能流量监测、控制、管理与优化设备,集成传统的带宽管理(QoS)、负载均衡、网络行为管理、集流量清洗、广域网加速五大功能为一体,整合式的网络边界管理平台可让用户在网络边界处如释重负。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

网络

+关注

关注

14文章

7560浏览量

88748 -

局域网

+关注

关注

5文章

751浏览量

46277 -

监测

+关注

关注

2文章

3601浏览量

44515

发布评论请先 登录

相关推荐

#硬声创作季 #FPGA 玩转FPGA-19 BJ-EPM240实验12-MAX II的UFM模块使用实例-1

fpgaEPM实例epM240

水管工

发布于 :2022年10月29日 12:33:38

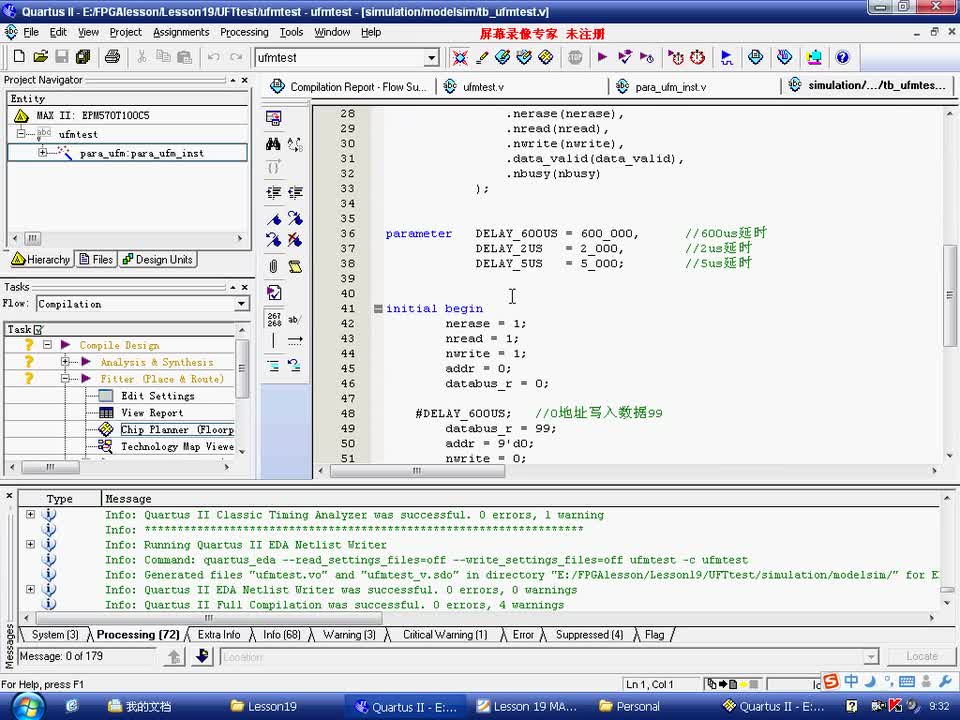

#硬声创作季 #FPGA 玩转FPGA-19 BJ-EPM240实验12-MAX II的UFM模块使用实例-2

fpgaEPM实例epM240

水管工

发布于 :2022年10月29日 12:34:00

让没有晶振的生活成为可能——UFM

传闻说CPLD有个缺陷,就是内部没有存储模块,所以不能对RAM,ROM等操作,但其实,CPLD内部有8192bits的UFM—Usr Flash Memory,很容易就可以实现RAM、ROM 的功能

发表于 01-17 10:41

基于VHDL的FPGA与NIOS_II实例精炼代码实例下载

http://115.com/file/ant54869#《基于VHDL的FPGA与NIOS_II实例精炼》第七章代码.rarhttp://115.com/file/e7wphx31#《基于VHDL

发表于 02-06 11:27

max2的ufm怎么用

有没有人知道altera公司的cplde器件max2的UFM怎么用i2c协议来读写。貌似用quartus建的一个ufm模块 只有 a2,a1,wp三个input和scl,sda2个in

发表于 10-27 12:13

MAX+Plus ii 软件

我最近在用MAX II系列下的芯片EPM240T100C5N,由于是新手就选择了MAX+Plus ii 这个软件,请问大家一下,这个软件支持选择MA

发表于 11-19 21:33

关于MAX II上电和复位的讨论

在使用MAX II给用户做替代模块的过程中,出现了一些很诡异的状况,这些状况也往往发生在上电伊始。因此,特权同学特别的花心思好好研究了一下MAX I

发表于 05-16 15:44

•2038次阅读

如何调试存储在Max 10开发套件片上闪存中的代码

我们可以创造一个从UFM就地执行的Nios II应用,并使用Nios II软件构建工具中的调试工具调试存储在UFM中的代码。先创建一个Quartus项目和Qsys系统,如下图,这是一个

FPGA视频教程之MAX.II的UFM模块使用实例详细资料说明

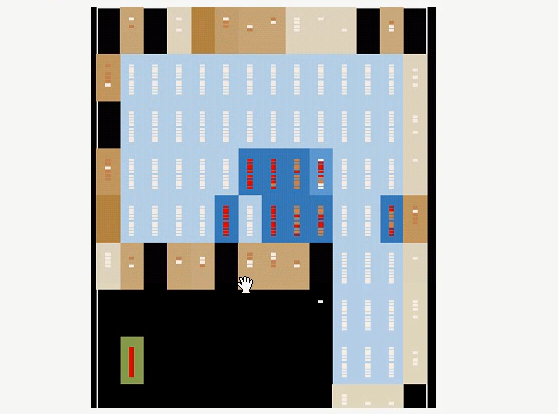

查看MAX II器件的Chip Planner 如图所示。其左下角这块黑色区域是用户不可用资源区,而在这片不可用区域里有一块绿色的方块是可用的。这块不可用的黑色区域叫做CFMblock(配置Flash存储区),而那个绿色方块叫做UFM

发表于 03-05 10:31

•5次下载

MAX.II的UFM模块使用实例

其左下角这块黑色区域是用户不可用资源区,而在这片不可用区域里有一块绿色的方块是可用的。这块不可用的黑色区域叫做CFM block(配置Flash存储区),而那个绿色方块叫做UFM(用户可用的Flash存储区)。对于后者是我们今天讨论的重点,先看以下官方对此存储区作用的描述

FPGA视频教程:BJ-EPM240学习板-MAX II的UFM模块使用实验

MAX II 器件属于非易失、瞬时接通可编程逻辑系列,采用了业界突破性的 CPLD 体系结构。这种体系结构帮助您大大降低了系统功耗、体积和成本。

MAX II设备系列数据

本节为设计师提供MAX®II设备的数据表规格。本章包含内部架构(architecture)、联合测试行动(Joint Test Action)的功能定义组(JTAG)和系统内可编程性(ISP)信息,DC操作MAX

发表于 09-29 10:21

•0次下载

MAX II的UFM模块使用实例

MAX II的UFM模块使用实例

评论