触发器是顺序电路的基本构建模块,可以从一种形式转换为另一种形式,能够存储单个数据位

我们在整个电子教程部分已经看过顺序逻辑触发器将无限期地保持其两种稳定状态之一,直到应用某种形式的外部触发脉冲使其改变状态。

作为触发器是双稳态器件,这些时序电路有时被称为“锁存器”,因为它们的输出被锁定或锁存到其输入状态,直到其输入条件发生另一次变化。

我们还看到双稳态翻转 - 触发器是时序逻辑电路中最基本的存储元件,并且可以配置为通过互连两个反相门来产生简单的存储器元件以产生反馈。注意,组合逻辑电路不需要任何形式的存储器,因此不使用触发器。然而,时序逻辑电路确实具有存储器,因此使用各种类型的触发器设计来记住它们的当前状态。

数字逻辑门的互连以产生存储器件导致诸如开关去抖电路的应用此外,由双稳态锁存器构成的存储器元件构成了累加器和寄存器的基础,计算机或微控制器在其上进行复杂的算术运算。

创建单个一位触发器的最基本方法是使用两个 NOR门门,如图所示。通过使用交叉耦合门并将输出从一个门馈送到另一个门的输入端(输入 - 输出互换),电路具有闭环(正反馈),因此其输出取决于输入的状态,使得电路顺序并具有存储器。

触发器也属于一类称为多谐振荡器的数字开关电路。基本双稳态多谐振荡器是一种再生电路,具有两个有源数字门,设计成当一个数字门导通时,另一个门被截止,反之亦然。这两个数字门产生两个稳定的输出,包括HIGH和LOW,其中一个是另一个的补码。

但我们可以制作许多不同类型的异步和同步触发器电路(异步翻转 - 触发器不需要时钟信号输入,但是同步的那个来自基本的交叉耦合NANDGates和NORGates,不同类型之间的触发器的转换有时会有点混乱。

基本上有四种不同类型的人字拖,这些是:

1。置位复位(SR)触发器或锁存器

2。 JK触发器

3。 D(数据或延迟)触发器

4。 T(Toggle)触发器

为了帮助我们更好地理解可用的不同类型的触发器,以下顺序逻辑教程向我们展示了如何进行触发器的转换简单地通过修改从SR触发器开始的特定类型触发器的输入,从一种类型到另一种类型。

Set-Reset SR触发器

所有双稳态锁存器和双稳态多谐振荡器中最基本的是置位(SR)触发器。基本的SR触发器是一个重要的双稳态电路,因为所有其他类型的触发器都是由它构建的。 SR触发器使用两个交叉耦合数字 NAND门构建,例如TTL 74LS00,或两个交叉耦合数字 NOR门,例如TTL 74LS02。 / p>

通常认为SR双稳态和触发器是透明的,因为它们的输出会改变或立即响应其输入的变化。此外,由于它们由数字逻辑门和反馈组成,因此SR触发器被视为异步时序逻辑电路。

基本SR触发器有两个输入 S (设置)和 R (复位)和两个输出 Q 和 Q ,其中一个输出是另一个的补充。然后SR触发器是双输入,双输出设备。考虑下面的电路。

基本NAND和NOR SR触发器

以上是使用负输入 NAND 门或正输入 NOR 门的异步SR双稳态触发器的两种基本配置。对于使用两个交叉耦合 NAND 门的SR双稳态锁存器,两个输入通常为高电平,逻辑电平为“1”。

在逻辑电平“0”施加低电平当 R 保持为高电平时 S 输入使输出 Q 变为高电平,设置锁存器。同样,输入 S 保持为高电平的 R 输入上的逻辑电平“0”会使 Q 输出变为低电平,从而复位锁存器。对于SR与非门锁存器,禁止 S = R = 0 的条件。

使用两个交叉耦合 NOR来触发触发器的转换

gate,当输出 Q = 1 且 Q = 0 时,双稳态锁存器被称为处于置位状态。当 Q = 0 且 Q = 1 时, NOR 门锁存器被称为处于复位状态。然后我们可以看到 NOR 和 NAND 门触发器的操作基本上只是彼此的补充。

执行使用两个交叉耦合 NAND 门的SR触发器需要低输入。但是,我们可以通过使用逆变器将 NAND SR触发器的操作转换为与 NOR 门实现相同的方式,具有有效HIGH(正逻辑)输入,( NOT Gates )在基本双稳设计中。

然后将触发器从低电平有效转换为有效高电平输入的方式如下:

有效HIGH触发器

上面的基本SR触发器及其高效的HIGH等效,都是异步类型触发器,意味着它的输入和当前状态决定了下一个状态。但作为一位存储器存储器件,我们可能希望它保持其当前输出状态,而不管其两个输入发生了什么,并且可以通过包含额外输入来修改基本SR触发器的操作来控制其行为。双稳态电路。

触发器基本电路的转换是通过使用两个额外的 AND 门来实现的,它们与控制输入一起启用和禁用 S 和 R 输入。这个新电路称为时钟或门控SR触发器。

门控置位 - 复位(SR)触发器

门控SR触发器按顺序操作,其输出状态仅响应其在时钟应用或使能输入上的输入而改变。由于通过该时钟使能输入控制输出的改变,所以门控SR触发器电路被称为“同步”触发器。然后异步SR触发器不需要时钟,但是同步的那个。

基于标准 NOR 的SR触发器到门控SR触发器的转换是使用连接到置位和复位输入的两个 AND 门(TTL 74LS08)实现。附加控制或“启用”输入 EN 连接到 AND 门,当时钟输入为低电平时,输出为低电平,如图所示。

门控SR触发器电路

时钟或使能输入, EN 连接到两个 AND 门的两个输入之一,当使能输入为低电平(AND门控原则)时,产生低电平输出。然后,对输入 S 或 R 的任何更改都不会影响输出的状态, Q 和 Q 触发器。

当使能输入为高电平时,两个 AND 门变为透明,因此对输入 S 和 R的任何更改将像以前一样改变输出的状态。然后我们可以看到逻辑电平“1”(高电平)或“0”(低电平)可以通过向时钟使能输入施加高电平来存储在门控触发器的输出端,并且该输出当启用输入保持为低电平时,无论输入条件如何,状态都可以保留任何所需的时间段。

门控触发器符号

由于门控SR触发器是三输入设备,逻辑符号显示三个输入: S , R 和 EN 。 EN 输入标有一个小三角形,表示触发器响应边沿或转换输入。

触发器转换为时钟触发器通过简单地将该使能输入连接到定时信号来实现。输出状态的任何变化都将与时钟 CLK 信号同步发生。注意,时钟信号被定义为一系列连续脉冲,每个脉冲具有两个独立的状态,即“ON”状态和“OFF”状态,其占空比代表其“ON”时间除以总的时间周期。脉冲,(“ON”时间+“OFF”时间)。几乎所有数字时钟信号都具有50%的占空比。

时钟SR触发器可以在时钟信号的上升沿或下降沿或脉冲的下降沿改变状态。因此,当时钟脉冲从一个电平变为另一个电平时,边沿触发的触发器仅响应或改变状态。例如,HIGH到LOW或LOW到HIGH。

正边沿触发触发器的输出仅在时钟脉冲的上升沿(0到1)改变状态而不是应对下降的负边缘。同样,负边沿触发的触发器在时钟脉冲的下降沿(1到0)改变状态,并且不响应上升的正沿。

门控SR触发器预设和清除

我们可以进一步采用这个门控SR触发器电路来生成一个双稳态锁存器,其中包含额外的输入,称为预设和清除输入可用于将触发器设置为独立于时钟的初始状态。我们可以覆盖所有输入并将输出预设为已定义的状态,而不是输出 Q 和 Q 加载未定义的值。

<但是,为什么我们要这样做呢?当电源首次施加到触发器电路时,输出的初始逻辑状态可以完全随机,这取决于首先锁存哪个逻辑门,然后我们不知道触发器电路处于哪个开关状态。因此触发器的初始状态是不确定的,因为它可能处于SET状态,( Q = 1 )或者它可能处于RESET状态,( Q = 0 预设, PR 和清除, CLR 如图所示。

具有预设和清除输入的触发器

>

当CLEAR输入为“0”且PRESET输入为“1”时,这些附加输入允许清除触发器( Q = 0 ) ”。同样,只要PRESET输入为“0”且CLEAR输入为“1”,触发器就可以预置为逻辑“1”状态。在此示例中,如果PRESET和CLEAR输入为高电平有效( P = CLR = 1 ),则电路作为普通门控SR触发器电路工作。很明显,PRESET和CLEAR输入不应同时处于低电平有效( P = C = 0 ),因为这会导致状态不确定。

此PRESET和CLEAR如果我们想要在准备下一个序列的顺序操作期间将触发器置于已知的置位或复位状态,那么选项也很方便。

将触发器从一种类型转换为另一种类型通过修改连接或使用额外的门很容易实现。正如我们所看到的,基本的SR触发器有两个输入, S 和 R 来存储单个位,但要做到这一点,我们必须同时激活这两个输入。此外,禁止输入组合: S = R = 1 可能会意外发生,从而导致SR触发器切换到未定义状态。

消除对两个独立的输入和无意切换到不确定状态的可能性,通过在置位和复位输入之间连接一个反相器(非门),我们可以将基本的RS触发器转换为D型触发器。

(数据)D型触发器

D型触发器或数据锁存器只有一个输入,称为“D”,或数据输入,加上时钟输入, CLK 以及通常的两个输出, Q 和 Q 。在延迟一个时钟脉冲之后,D型触发器在输入和输出之间传输其数字数据,因此“D”部分也称为“延迟”输入。

通过简单地连接 S 和 R 输入之间的反相器,可以轻松地从SR触发器构建D型触发器,从而连接到逆变器的输入到 S 输入,并且变频器的输出连接到 S 输入,如图所示。

D型触发器

上面给出了将触发器转换为D型的两种不同电路。顶部电路是传统的门控D型配置,带有额外的逆变器。底部电路以完全相同的方式工作,但没有逆变器,节省了一个门。与所有触发器配置一样,D型触发器可以使用 NAND 或 NOR 门实现,无论是否有额外的预设和清除。

在输入之间使用逆变器可确保 S 和 R 输入始终是彼此的补充,从而消除了以下不确定条件: S = R = 1 。因此,D型触发器也称为“透明锁存器”,因为当时钟输入为高电平时输出 Q 跟随 D 输入, CLK = 1 将输入端的二进制信息直接传送到输出端,就像触发器不存在一样,使其透明。

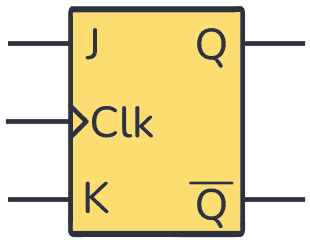

JK触发器

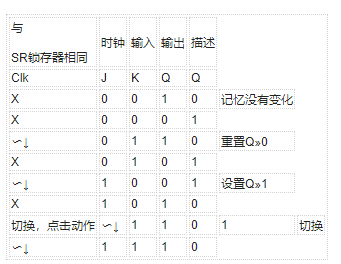

JK触发器在许多方面与之前的SR触发器非常相似,可能是所有触发器设计中使用最多的。术语“J”和“K”并不真正意味着或涉及任何特殊描述,而是最初在触发器初始开发时使用的,因为这两个字母不用作任何其他数字设备的一部分。对于JK触发器,“J”相当于Set,“K”相当于Reset。

我们之前看到SR触发器有两个或者可能有三个有意义的输入组合不允许 S = R = 1 组合的输入序列,但可以轻松修改它以实现不同的切换功能。然后JK触发器通常被认为是通用器件。

JK触发器有两个输入“J”和“K”,因此所有四种可能的输入配置:无变化,设置,重置和切换有效。 “J”输入的作用类似于“S”,“K”输入的作用类似于“R”,当其中一个输入为高电平时,它会改变状态。然而,JK触发器的优点在于,当“J”和“K”都为逻辑“1”时为高电平时,触发器会切换,即从“0”变为“1”或从“1”变为“1”。 “到”0“产生自己的补充状态。

JK触发器电路

将触发器转换为JK触发器是通过额外的3输入将 Q 和 Q 输出与 S 和 R 输入交叉连接AND 门如图所示。

如果 J 和 K 输入都为HIGH,逻辑“1”则为 Q只要时钟输入( CLK )为HIGH,输出就会改变状态(Toggle)。因此,输出将是不稳定的,从而产生这种基本JK电路的竞争问题。通过确保时钟输入仅在非常短的时间内处于逻辑“1”,或者产生称为主从触发器的更复杂的JK触发器电路,可以避免这个问题。

主从触发器

将触发器转换为“主从”配置涉及添加第二双稳态电路。主从配置由两个级联连接的SR锁存器组成。一个双稳态触发器作为主器件接收外部输入,而另一个作为其从器件,直接从主触发器获取其输入,如图所示。

基本主从配置

当时钟 CLK 脉冲变为高电平时, S 和 R 输入正常通过主触发器 FF A 传输。然而,相邻的从触发器 FF B 保持隔离,因为其时钟输入, CLK 为低电平,逻辑“0”由于反转通过反相器。

现在当初始时钟脉冲返回LOW为“0”时,主机被禁用并阻止外部数据输入传递信息到其输出,而从机触发器现在变为启用状态并因此将锁存的信息传递到 Q 和 Q 的输出。然后输入到从触发器的时钟是主触发器的时钟输入的补充。

主从触发器被称为电平触发或脉冲触发双稳态,因为在输入时钟脉冲处于高电平的整个时间内读取输入数据。此外,主从触发器不仅限于SR主从。还有JK主从和D型主从触发器。在几乎所有的触发器中,从触发器都是标准的SR触发器,而触发器的类型则来自主器件,它将是SR,JK或D型配置。

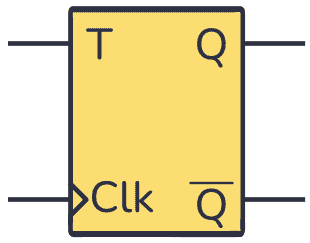

(Toggle)T型触发器

T型(切换)触发器是单输入双稳态,其操作类似于上面的D型。我们在上面看到了JK触发器配置,如果 J = K = 1 ,它的输出将在下一个时钟周期的应用中切换。然后将触发器转换为Toggle类型只是将输入连接为HIGH的问题。

T型触发器在商业上不可用,但可以用JK触发器构建(或者,通过将 J 输入与 K 输入连接,并将两者都连接到逻辑电平“1”,或者D型触发器。当 J 且 K 为高电平时,触发器每次在其时钟输入触发时都会改变状态。此时钟输入现在称为“切换输入”,如果输出变为“1”则为“1”,如果为“1”则输出为“0”,即切换为“0”。

切换T型触发器

当应用时钟输入时,切换触发器改变状态, T = 1 并在 T = 0 时保持不变。然后从“0”到“1”的转换将导致输出切换,为触发器命名。拨动T型触发器是许多数字电路的基本构建模块,包括分频器和数字计数器。

Toggle T型触发器可以用两种简单的方式从JK触发器构造。首先, J 和 K 输入可以连接在一起,如图所示,时钟输入变为切换,如图所示。第二种方法是将 J 和 K 输入连接在一起,以提供切换输入,时钟输入保持不变。当 T 和 CLK =或等于“1”时,输出切换。当 T 或 CLK 为低电平时,输出保持不变。

数据D型触发器可以像JK触发器一样转换通过将 Q 输出直接连接到D输入,并将切换信号 T 作为时钟输入,如上所示,作为触发器执行。将 Q 连接到输入会产生负反馈。

由于来自切换触发器的输出在每次应用时钟信号时改变状态,因此其输出频率为 - 输入信号频率的一半,从而充当分频器。如果更多的触发触发器级联在一起形成一个链,因为第一个触发器的输出充当级联排列中第二个T触发器的时钟,第二个触发器充当时钟输入对于第三个T触发器等,沿链创建一个分频。

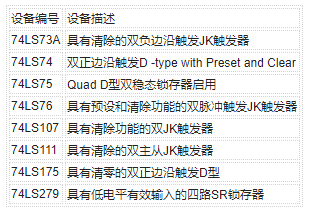

触发器和锁存器是顺序逻辑电路最基本的构建模块。因此,许多IC制造商生产各种不同的触发器芯片,使用下面列出的TTL和CMOS技术。

流行的触发器IC类型

触发器转换摘要

我们在本教程中已经看到双稳态设备是存在两个明确定义的状态的设备,并且设备可以随时采用任一稳定状态。触发器从一种类型到另一种类型的转换可以非常容易地完成,因为只需要稍微修改就可以将一种类型转换成另一种类型。可以使用带反馈的逻辑门电路构建触发器。

我们还看到触发器可以有一个,两个或三个输入,其中一个输入连接到时钟信号。所有触发器都有两种输出状态: Q = 1 和 Q = 0 ,它们响应时钟的应用而变化。对于SR锁存器, S = 1 设置 Qto1 , R = 1 重置 Qto0 。

JK触发器被归类为通用触发器,其设计与SR触发器类似,当 J = 1 时,它设置 Qto1 ,当 K = 1 时,它会重置 Qto0 。条件 J = K = 1 导致 Q 切换。

上面讨论的所有触发器都可以有额外的异步CLEAR和PRESET输入,使 Q 被清除为“0”或预设为“1”,与时钟信号无关。 / p>

D型双稳态可以通过在 J 和 K 输入之间增加一个逆变器来构建JK触发器。 D型触发器广泛用于数字系统以传输数据,据说是透明的,因为输入中的任何机会都会被立即接受,输出也会相应改变。

T或切换翻转 - 当 T = 1 时,翻转会改变应用时钟脉冲的状态,否则 Q 不会改变。触发器触发器通常用于分频或设计二进制计数器,因为二进制计数器需要互补。切换触发器不是商用的,但可以通过将JK触发器的 J 和 K 输入连接在一起来实现。

通过重新配置输入或通过添加额外的逻辑门,通常可以将触发器从一种类型转换为另一种类型,我们已经看到SR触发器可以转换为JK触发器本身可以转换为数据锁存器,JK触发器和D型都可以转换为T型触发器。

-

逻辑门

+关注

关注

1文章

142浏览量

24145 -

算术运算

+关注

关注

0文章

6浏览量

5711 -

人字拖

+关注

关注

0文章

2浏览量

6858

发布评论请先 登录

相关推荐

JK人字拖触发器和函数表

Impact Footwear推出下一代3D打印人字拖:个性化定制自己的拖鞋

具有清除和预设的双正边缘触发D型触发器SNx4LVC74A数据表

人字拖的转换触发器预设和清除配置类型摘要

人字拖的转换触发器预设和清除配置类型摘要

评论