有三种基本类型的数字逻辑门,AND门,OR门和NOT门

我们还看到每个门在其中具有相反或互补的形式NAND门,NOR门和缓冲器的形式,任何这些单独的门可以连接在一起形成更复杂的组合逻辑电路。

我们也看到,在数字电子学中NAND门和NOR门都可以归类为“通用”门,因为它们可以用于构造任何其他门类型。实际上,任何组合电路都可以仅使用两个或三个输入NAND或NOR门来构造。我们还看到NOT门和缓冲器是单输入器件,也可以具有三态高阻抗输出,可用于控制数据流到公共数据总线上。

数字逻辑门可以由分立元件组成,例如电阻,晶体管和二极管形式RTL(电阻 - 晶体管逻辑)或DTL(二极管 - 晶体管逻辑)电路,但今天的现代数字74xxx系列集成电路使用TTL (晶体管 - 晶体管逻辑)基于NPN双极晶体管技术或74Cxxx,74HCxxx,74ACxxx和4000系列逻辑芯片中使用的速度更快,功耗更低的CMOS晶体管逻辑。

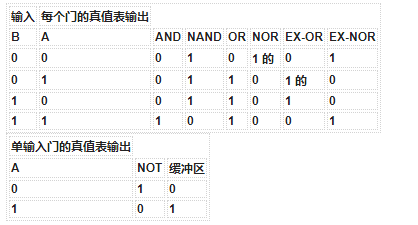

下面总结了八个最“标准”的数字逻辑门及其相应的真值表。

标准逻辑门

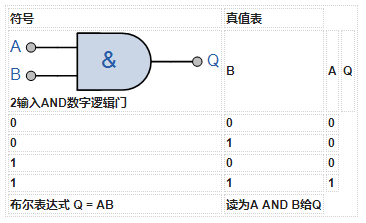

逻辑与门

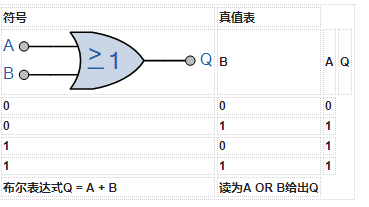

逻辑或门

反转逻辑门

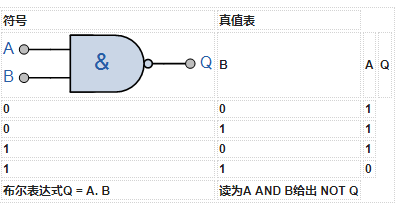

逻辑与非门

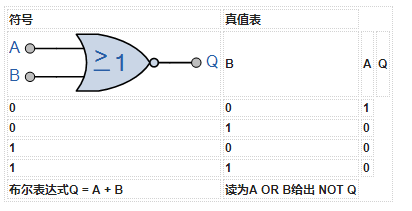

逻辑NOR门

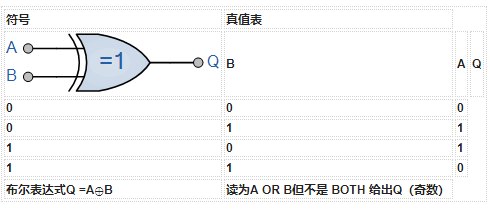

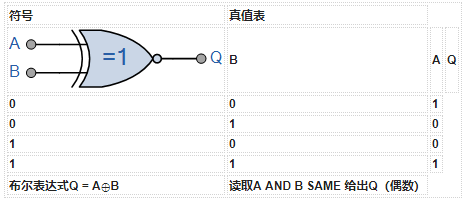

独占逻辑门

逻辑异或门(Ex-OR)

逻辑异或非门(Ex-NOR)

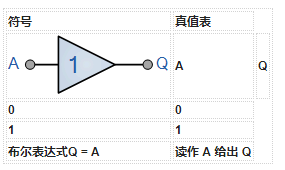

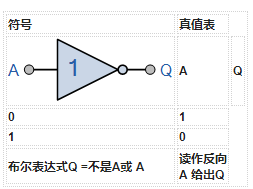

单输入逻辑门

十六进制缓冲区

NOT门(逆变器)

上面的数字逻辑门及其布尔表达式可以归纳为单个真值表,如下所示。该真值表显示了每个可能的输入组合的主数字逻辑门的每个输出之间的关系。

数字逻辑门真值表汇总

以下逻辑门真值表比较了上面详述的2输入逻辑门的逻辑功能。

上拉和下拉电阻

最后要记住的一点,当将数字逻辑门连接在一起以产生逻辑电路时,门的任何“未使用”输入必须通过适当的“上拉”或“直接”连接到逻辑电平“1”或逻辑电平“0”。下拉“电阻(例如1kΩ电阻)以产生固定逻辑信号。这将防止未使用的栅极输入“浮动”并产生门和电路的错误切换。

以及使用上拉或下拉电阻可防止未使用的逻辑门浮动,门和锁存器的备用输入也可连接在一起或连接到单个IC封装内的剩余或备用门,如图所示。

-

电路

+关注

关注

171文章

5545浏览量

170334 -

逻辑门

+关注

关注

1文章

130浏览量

23901 -

晶体管

+关注

关注

77文章

9181浏览量

136111

发布评论请先 登录

相关推荐

数字逻辑门总结功能

数字逻辑门总结功能

评论