二进制加法器是半加器和全加法器形式的运算电路,用于将两个二进制数字加在一起.

另一种常见且非常有用的组合逻辑电路,可以使用一些基本的逻辑门允许它将两个或多个二进制数加在一起是二进制加法器。

一个基本的二进制加法器电路可以用标准的 AND 和 Ex-OR 门允许我们将两个单位二进制数“加”到一起, A 和 B 。

添加这两个数字会产生一个名为 SUM 的输出,另一个输出称为 CARRY 或 Carry-out , (C OUT )位根据二进制加法规则。 二进制加法器的主要用途之一是算术和计数电路。考虑下面简单地添加两个denary(基数为10)的数字。

| 123 | A | (Augend) |

| +789 | B | (加数) |

| 912 | SUM |

从我们在学校的数学课程中,我们了解到每个数字列都已添加从右侧开始,每个数字的加权值取决于它在列中的位置。

当每个列加在一起时,如果结果大于或等于10,则生成进位,基数。然后将这个进位添加到左侧添加下一列的结果,依此类推,简单的学校数学的添加,添加数字和携带。

添加二进制数是完全相同的想法作为将十进制数加在一起的但是这次只有当任何列中的结果大于或等于“2”(二进制的基数)时才生成进位。换句话说, 1 + 1 会创建一个进位。

二进制加法

二进制加法遵循这些相同的基本规则。上面的否定加法除了二进制外,只有两位数,最大位为“1”。因此,当添加二进制数时,当“SUM”等于或大于2(1 + 1)时会生成执行,并且这将成为任何后续添加的“CARRY”位,然后传递到下一列进行添加,因此上。考虑下面的单位添加。

两位的二进制加法

| 0 | 0 | 1 | 1 |

| + 0 | + 1 | + 0 | + 1 |

| 0 | 1 | 1 | (carry)1←0 |

当两个单位, A 和 B 加在一起时,添加“0 + 0”,“0 + 1”和“1 +” 0“结果为”0“或”1“,直到您到达”1 + 1“的最后一列,然后总和等于”2“。但二进制不存在于二进制中,二进制中的2等于 10 ,换句话说,总和为零加上一个额外的进位。

然后操作一个简单的加法器需要两个数据输入,产生两个输出,等式的Sum(S)和一个Carry(C)位,如图所示。

二进制加法器框图

对于上面的简单1位加法问题,可以忽略得到的进位,但是你可能已经注意到了有关加法的其他内容这两位,它们的二进制加法的总和类似于异或门。如果我们将这两个位标记为 A 和 B ,则生成的真值表是两位的总和,但没有最终进位。

2输入异或门

| 符号 | 真相表 | ||

2输入异或门 |

B | A | S |

| 0 | 0 | 0 | |

| 0 | 1 | 1 | |

| 1 | 0 | 1 | |

| 1 | 1 | 0 |

我们可以从真值表中看到如上所述,当任一输入处于逻辑“1”时,异或门仅产生输出“1”,而不是与前两位的二进制加法相同。然而,为了执行两个数字的加法,微处理器和电子计算器需要额外的进位来正确计算方程式,因此我们需要重写先前的求和以包括两位输出数据,如下所示。

| 00 | 00 | 01 | 01 |

| +00 | + 01 | + 00 | + 01 |

| 00 | 01 | 01 | 10 |

从上面的等式我们现在知道一个异或门将当“EITHER”输入为逻辑“1”时,只产生输出“1”,因此当“BOTH”输入 A 和 B 处于逻辑“1”。当输入 A 和 B 均为“1”时,一个适合该账单的数字门完美地产生输出“1”( HIGH)是标准AND门。

2输入AND门

| 符号 | 真值表 | ||

2-input AND Gate |

B | A | C |

| 0 | 0 | 0 | |

| 0 | 1 | 0 | |

| 1 | 0 | 0 | |

| 1 | 1 | 1 |

通过combinin g带有 AND 门的异或门产生一个简单的数字二进制加法器电路,通常称为“Half Adder”电路。 / p>

半加法器电路

半加器是一个逻辑电路,对两个二进制数字执行加法运算。半加器产生一个和两个二进制数的进位值。

带进位的半加法真值表

| 符号 | 真值表 | |||

|

B | A | SUM | CARRY |

| 0 | 0 | 0 | 0 | |

| 0 | 1 | 1 | 0 | |

| 1 | 0 | 1 | 0 | |

| 1 | 1 | 0 | 1 |

从半加器的真值表中我们可以看到SUM( S )输出是异或门的结果,执行( Cout )是 AND <的结果/ span> gate。然后半加法器的布尔表达式如下。

对于SUM位:

SUM = AXORB = A ⊕ 乙

对于CARRY位:

CARRY = AANDB = AB

一个主要当用作二进制加法器时, Half Adder 电路的缺点是,当将多个数据位加在一起时,没有提供前一电路的“进位”。

例如,假设我们想要将两个8位字节的数据相加,任何产生的进位都需要能够从最低有效位(LSB)开始“波动”或移过位模式。半加器可以做的最复杂的操作是“1 + 1”,但由于半加器没有进位输入,因此得到的附加值是不正确的。解决此问题的一种简单方法是使用Full Adder型二进制加法器电路。

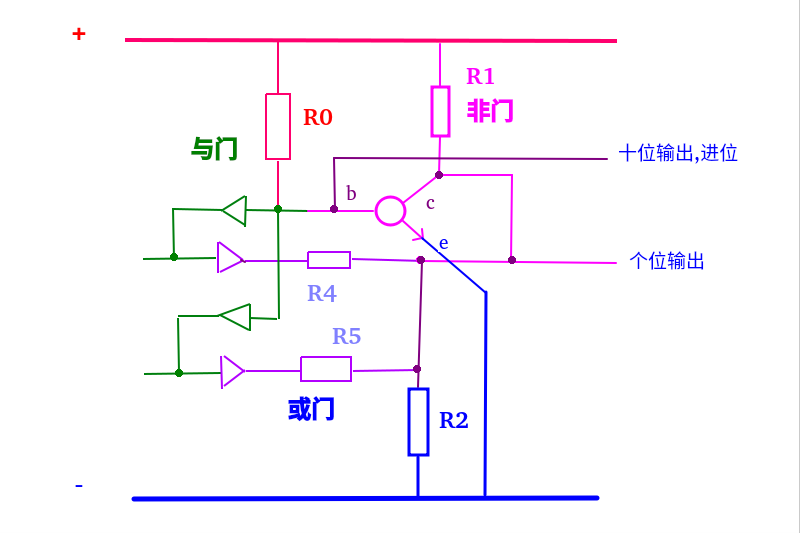

全加器电路

> Full Adder和之前的Half Adder是全加器有三个输入。与以前相同的两个单位数据输入 A 和 B 加上一个额外的进位( C-in )输入以接收来自前一阶段的进位,如下所示。

Full Adder Block Diagram

然后全加器是合乎逻辑的对三个二进制数字执行加法运算的电路,就像半加法器一样,它也会产生一个进位到下一个加法列。然后 Carry-in 可能来自不太重要的数字,而 Carry-out 表示进位到更高位数。

在许多方面,全加器可以被认为是连接在一起的两个半加法器,前半部加法器将其进位传递到后半部加法器,如图所示。

全加法逻辑图

由于上面的全加器电路基本上是连接在一起的两个半加法器,因此全加器的真值表包含一个附加列考虑进位, C IN 输入以及总和输出 S 和进位-out, C OUT 位。

带有进位的全加法真值表

| 符号 | 真值表 |

| C-in | B | A | 总和 | C-out | |

| 0 | 0 | 0 | 0 | 0 | |

| 0 | 0 | 1 | 1 | 0 | |

| 0 | 1 | 0 | 1 | 0 | |

| 0 | 1 | 1 | 0 | 1 | |

| 1 | 0 | 0 | 1 | 0 | |

| 1 | 0 | 1 | 0 | 1 | |

| 1 | 1 | 0 | 0 | 1 | |

| 1 | 1 | 1 | 1 | 1 |

然后全加器的布尔表达式如下。

对于SUM( S )位:

SUM =(AXORB)XORCin =(A ⊕ B)⊕ Cin

对于CARRY-OUT( Cout )位:

CARRY-OUT = AANDBORCin(AXORB)= A.B + Cin(A ⊕ B)

n位二进制加法器

我们已经看到上面的单个1位二进制加法器可以是从基本逻辑门构造。但是,如果我们想要将两个 n位数字加在一起,那么 n 数量的1位全加器需要连接或“级联”在一起产生什么是称为纹波进位加法器。

“纹波进位加法器”只是“ n ”,1位全加器与每个完整级联加法器表示长二进制加法中的单个加权列。它被称为纹波进位加法器,因为进位信号通过二进制加法器从右到左产生“纹波”效应(LSB到MSB)。

例如,假设我们想要将两个4位数字“加”在一起,第一个全加器的两个输出将提供加法的第一位数字和( S )加上a进位位作为下一个二进制加法器的进位数。

链中的第二个二进制加法器也产生求和输出(第2位)加上另一个进位位,我们可以继续向组合中添加更多的完整加法器以添加更大的数字,将第一个完整二进制加法器的进位位输出链接到下一个完整加法器,依此类推。下面给出了一个4位加法器的例子。

一个4位纹波进位加法器

将1位二进制加法器“级联”以添加大二进制数的一个主要缺点是,如果输入 A 且 B 更改,其输出的和将无效,直到任何进位输入已“链接”到链中的每个完整加法器,因为总和的MSB(最高有效位)必须等待来自进位输入的任何更改LSB(不太重要的位)。因此,在加法器的输出响应其输入的任何变化导致累积延迟之前将存在有限的延迟。

当添加的位的大小不是太大时,例如,4或8位,或加法器的求和速度并不重要,这种延迟可能并不重要。但是,当比特的大小较大时,例如在多比特加法器中使用的32或64比特,或者在非常高的时钟速度下需要求和时,这种延迟可能会变得非常大,因为在一个加法过程中没有正确地完成加法过程。时钟周期。

这个不需要的延迟时间称为传播延迟。当 n位加法器将两个并行数加在一起时,另一个问题称为“溢出”,其总和大于或等于 2 n

一种解决方案是直接从 A 和 B 输入生成进位输入信号,而不是使用上面的纹波排列。然后产生另一种类型的二进制加法器电路,称为Carry Look Ahead Binary Adder,其中使用进位超前逻辑可以大大提高并行加法器的速度。

优点进位前瞻加法器的一个特点是,为了产生正确的SUM,进位前瞻加法器所需的时间长度与操作中使用的数据位数无关,这与并行纹波加法器需要完成SUM的周期时间不同这是加数中总位数的函数。

具有进位超前功能的4位全加器电路可作为标准IC封装以TTL 4位二进制加法器74LS83的形式提供或者74LS283和CMOS 4008可以将两个4位二进制数加在一起并生成 SUM 和 CARRY 输出,如图所示。

74LS83逻辑符号

二进制加法器摘要

我们在本教程中已经看到二进制加法器那个加法器电路c用于“加”两个二进制数,产生“执行”。在最基本的形式中,加法器可以通过将异或门与 AND 门连接在一起来产生半加法器电路。可以组合两个半加法器来产生Full Adder。

有许多4位全加器IC可用,例如74LS283和CD4008。这将添加两个4位二进制数并提供一个额外的输入进位,以及一个输出进位,因此您可以将它们级联在一起以产生8位,12位,16位加法器,但进位传播延迟可能是大型n位纹波加法器中的主要问题。

-

加法器

+关注

关注

6文章

183浏览量

30365 -

二进制加法器

+关注

关注

0文章

3浏览量

3317

发布评论请先 登录

相关推荐

加法器电路原理图解_二进制加法器理解

二进制加法器电路框图

二进制加法器电路框图

评论