MOD计数器是级联计数器电路,在复位前计数到设定的模数值

计数器的工作是通过每个时钟脉冲将计数器的内容提前一个计数来计数。当被时钟输入激活时推进其数字或状态序列的计数器被称为以“递增计数”模式操作。同样,当被时钟输入激活时减少其数字或状态序列的计数器被称为以“倒计数”模式操作。在UP和DOWN模式下工作的计数器称为双向计数器。

计数器是由外部定时脉冲或时钟信号激活或触发的时序逻辑器件。计数器可以构造成用作同步电路或异步电路。对于同步计数器,所有数据位与时钟信号的应用同步变化。而异步计数器电路独立于输入时钟,因此数据位在不同的时间一个接一个地改变状态。

然后计数器是顺序逻辑设备,遵循预定的计数状态序列,由外部时钟(CLK)信号。在再次返回其原始第一状态之前特定计数器通过其前进的状态或计数序列的数量称为模数(MOD)。换句话说,模数(或仅模数)是计数器计数的状态数,是计数器的除数。

模数计数器,或者只是 MOD计数器是根据计数器在返回其原始值之前排序的状态数定义的。例如,一个2位计数器,从二进制的00 2 到11 2 计数,即十进制的0到3,其模数值为4(00→ 1→10→11,然后返回00)因此称为modulo-4或mod-4计数器。另请注意,它需要四个时钟脉冲才能从00到11。

在这个简单示例中,只有两位,(n = 2),然后是最大可能输出状态数(最大模数) )对于计数器是:2 n = 2 2 或4.但是,计数器可以设计为计数到任何数量的2 n 状态通过将多个计数阶段级联在一起产生单个模数或MOD-N计数器。

因此,“Mod-N”计数器将需要连接在一起的“N”个触发器来计数单个数据位同时提供2个 n 不同的输出状态,(n是位数)。注意,N总是一个整数值。

我们可以看到MOD计数器的模数值是2的整数幂,即2,4,8,16等等。产生一个n位计数器,具体取决于所用触发器的数量,以及它们的连接方式,确定计数器的类型和模数。

D型触发器

MOD计数器使用“触发器”制作,单个触发器可以产生0或1的计数,最大计数为2.我们可以使用不同类型的触发器设计,SR, JK,JK主从,D型甚至T型触发器构成一个计数器。但为了简单起见,我们将使用D型触发器(DFF),也称为数据锁存器,因为使用单个数据输入和外部时钟信号,并且也是正边沿触发。

D型触发器,如TTL 74LS74,可以由基于SR或JK的边沿触发触发器制成,具体取决于您是希望它在正边沿还是在前沿处改变状态(0时钟脉冲的负或后沿(1到0转换)或1转换。在这里,我们假设一个正的,前沿触发的触发器。您可以在以下链接中找到有关D型触发器的更多信息。

D型触发器和真值表

D型触发器(DFF)的操作非常简单,因为它只有一个数据输入,称为“D”,另外一个时钟“CLK”输入。这允许在时钟信号的控制下存储单个数据位(0或1),从而使D型触发器成为同步器件,因为输入上的数据仅传输到触发器输出触发时钟脉冲的边沿。

因此,从真值表中,如果在施加正时钟脉冲时数据输入上存在逻辑“1”(高电平),触发器SET和存储器“Q”处的逻辑“1”和 Q 处的互补“0”。同样,如果在施加另一个正时钟脉冲时数据输入上有一个低电平,触发器RESET会在“Q”处存储“0”,在 Q 处产生“1” 。

然后,当时钟(CLK)输入为高电平时,D型触发器的输出“Q”响应输入“D”的值。当时钟输入为低电平时,保持“Q”状态,“1”或“0”,直到下一次时钟信号变为高电平为逻辑电平“1”。因此,“Q”的输出仅在时钟输入从“0”(低)值变为“1”(高)时改变状态,使其成为正边沿触发的D型触发器。请注意,负边沿触发的触发器工作方式完全相同,只是时钟脉冲的下降沿是触发边缘。

所以现在我们知道边缘触发的D型触发器是如何翻牌工作,让我们看看连接在一起形成一个MOD计数器。

除以两个计数器

边缘触发的D型触发器是一个有用的多功能构建块以构建MOD计数器或任何其他类型的顺序逻辑电路。通过将 Q 输出连接回“D”输入,如图所示,并创建一个反馈环路,我们可以将它转换为二进制二分频计数器,仅使用时钟输入作为 Q 输出信号始终是Q输出信号的反相。

除以二计数器和时序图

时序图显示“Q”输出波形的频率恰好是时钟输入的一半,因此触发器充当分频器。如果我们添加另一个D型触发器使得“Q”的输出是第二个DFF的输入,那么来自第二个DFF的输出信号将是时钟输入频率的四分之一,依此类推。因此,对于“n”个触发器,输出频率除以2n,步长为2.

注意,这种分频方法非常便于在顺序计数电路中使用。例如,通过使用60分频计数器,可以将60Hz电源频率信号降低到1Hz定时信号。 6分频计数器将60Hz降低到10Hz,然后输入到10分频计数器,将10Hz分频为1Hz定时信号或脉冲等。

MOD- 4计数器

从技术上讲,作为1位存储设备,单个触发器本身可以被认为是MOD-2计数器,因为它有一个输出导致计数在应用时钟信号时,有两个,0或1。但是单个触发器本身产生有限的计数序列,因此通过将更多的触发器连接在一起形成链,我们可以增加计数能力并构建任何值的MOD计数器。

如果单个触发器可以被认为是模2或MOD-2计数器,那么添加第二个触发器将为我们提供一个MOD-4计数器,允许它在四个不连续的步骤中计数。总体效果是将原始时钟输入信号除以4。然后,这个2位MOD-4计数器的二进制序列将是:00,01,10和11,如图所示。

MOD-4计数器和时序图

注意,为简单起见,上述时序图中的QA,QB和CLK的开关转换显示为同时,即使此连接表示异步计数器。实际上,正向时钟(CLK)信号的应用与QA和QB的输出之间的切换延迟非常小。

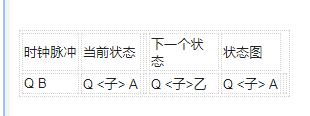

我们可以直观地显示这个2位异步的操作计数器使用真值表和状态图。

MOD-4计数器状态图

我们可以从计数器的真值表中看到,并通过读取QA和QB的值当QA = 0且QB = 0时,计数为00.应用时钟脉冲后,值变为QA = 1,QB = 0,计数为01,在下一个时钟脉冲后,为v等于变为QA = 0,QB = 1,计数为10.最后,值变为QA = 1,QB = 1,计数为11.下一个时钟脉冲的应用导致计数返回到00,然后它以二进制序列连续计数:00,01,10,11,00,01 ......等等。

然后我们看到一个MOD-2计数器由一个触发器组成一个MOD-4计数器需要两个触发器,允许它在四个不连续的步骤中计数。我们可以很容易地在MOD-4计数器的末端添加另一个触发器以产生一个MOD-8计数器,给出一个2 3 二进制序列,从000到111计数,然后重置为000.第四个触发器会产生一个MOD-16计数器,依此类推,实际上我们可以继续添加额外的触发器。

MOD-8计数器和状态图

因此我们可以构造mod计数器以具有自然计数在重复自身之前,2个 n 状态给出计数器的mod计数为2,4,8,16等。但有时需要一个模数计数器,在正常计数过程中将其计数重置为零,并且没有模数为2的幂。例如,模数为3,5,6的模数,或者10.

Modulo“m”的计数器

计数器,无论是同步还是异步,在一组二进制进程中一次进行一次计数,结果是“n”位计数器自然地作为模2 n 计数器。但是我们可以通过使用一个或多个外部逻辑门来构造mod计数器以计数到我们想要的任何值,使其跳过几个输出状态并在任何计数终止,将计数器重置为零,即所有触发器都具有Q = 0。

在模“m”计数器的情况下,它们不计入所有可能的状态,而是计数到“m”值然后返回到零。显然,“m”是小于2 n 的数字,(m <2 n)。那么我们如何让二进制计数器通过计数返回零部分。

幸运的是,除了计数,向上或向下,计数器还可以有额外的输入,称为 CLEAR 和 PRESET 可以将计数清零(所有Q = 0)或将计数器预设为某个初始值。 TTL 74LS74具有低电平有效预置和清零输入。

为简单起见,我们假设CLEAR输入全部连接在一起,并且是高电平有效输入,允许触发器在清除输入时正常工作。等于0(低)。但是如果清除输入处于逻辑电平“1”(高电平),则时钟信号的下一个上升沿将把所有触发器复位到状态Q = 0,而不管下一个时钟信号的值。 / p>

另请注意,由于所有Clear输入连接在一起,因此在计数开始之前,还可以使用单个脉冲将所有触发器的输出(Q)清零,以确保计数实际开始从零开始。此外,一些较大的位计数器还有一个额外的ENABLE或INHIBIT输入引脚,它允许计数器在计数周期的任何一点停止计数并保持其当前状态,然后再允许继续计数。这意味着可以随意停止和启动计数器,而无需将输出重置为零。

模数计数器

假设我们要设计一个MOD-5计数器,怎么可能我们这样做。首先我们知道“m = 5”,所以2 n 必须大于5.当2 1 = 2时,2 2 = 4 ,2 3 = 8,且8大于5,那么我们需要一个带有三个触发器(N = 3)的计数器,给出二进制的自然计数000到111(0到7)十进制)。

采用上面的MOD-8计数器,自然计数的真值表如下:

MOD-8计数器和真值表

当我们构建一个MOD-5计数器时,我们希望计数器在计数5后重置为零。但是,我们从附加的真值表可以看出,6的计数给出了输出条件:QA = 0,QB = 1,QC = 1.

我们可以解码这个输出状态011(6)在3输入与门(TTL 74LS11)和反相器或非门(TTL 74LS04)的帮助下,给我们一个清除(Clr)计数器信号的信号。

逆变器和AND门的组合逻辑电路的输入连接到QA,QB和QC相关对于除了我们想要的输入之外的任何输入组合,AND门的输出处于逻辑电平“0”(低)。

在二进制代码中,输出序列计数如下所示:000,001,010,011,100,101。但是当它达到011(6)状态时,组合逻辑电路将检测到这个011状态,产生逻辑电平为“1”(高电平)的输出。

然后我们可以使用AND门产生的HIGH输出,在输出5(十进制)计数后将计数器重置为零所需的MOD-5计数器。当组合电路的输出为低电平时,它对计数序列没有影响。

MOD-5计数器和真值表

然后我们可以在基本计数器周围使用组合逻辑解码电路,无论是同步还是异步,都可以产生我们要求的任何类型的MOD计数器,因为每个计数器的唯一输出状态都可以被解码以重置计数器处于所需的计数状态。

在上面的简单示例中,我们使用3输入AND门来解码011状态,但QA和QB第一次都处于逻辑1时是当计数达到6时,可以使用连接到QA和QB的2输入AND门,而不会使第3个输入和逆变器复杂化。

但是,使用异步计数器的一个缺点是产生所需计数的MOD计数器是当计数器达到其复位状态时可能发生称为“毛刺”的不希望的效应。在这短暂的时间内,计数器的输出可能采用不正确的值,因此有时最好将同步计数器用作模数计数器,因为所有触发器都由相同的时钟信号计时,因此同时改变状态。

模数10计数器

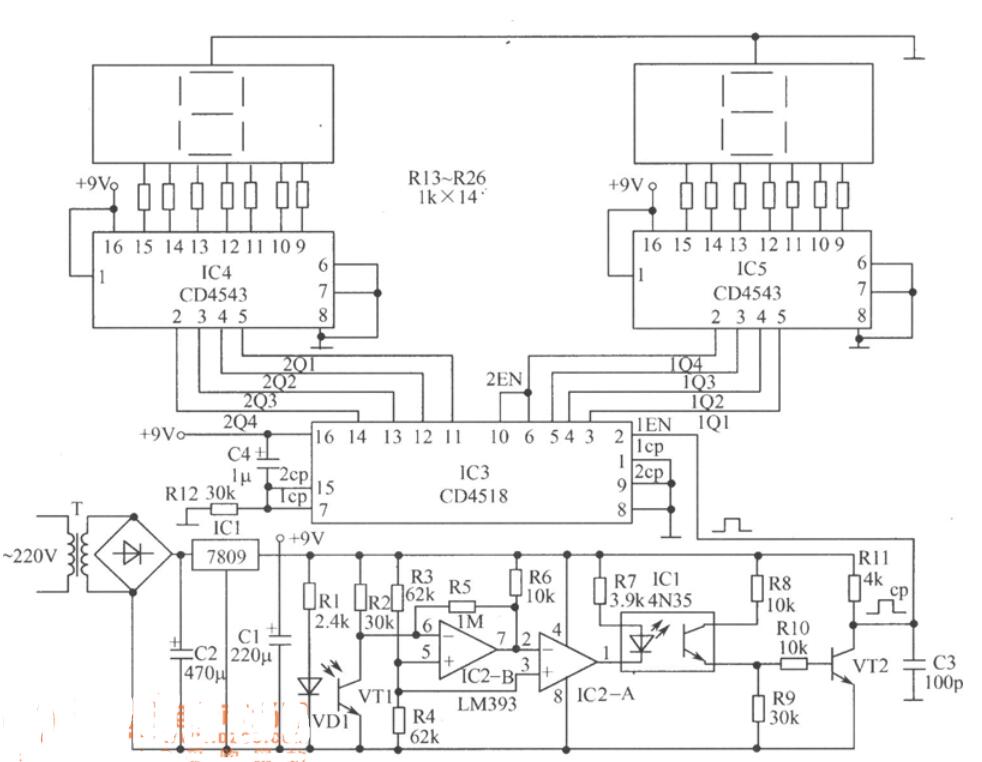

使用外部组合电路生成模数为10的计数器的模数计数器电路的一个很好的例子是十进制计数器。十进制(10分频)计数器,如TTL 74LS90,在其计数序列中有10个状态,使其适用于需要数字显示的人机接口。

十年计数器有四个输出产生一个4位二进制数,通过使用外部AND和OR门,我们可以检测到第9个计数状态的发生,将计数器重置为零。与其他mod计数器一样,它会逐个接收输入时钟脉冲,并重复从0到9递增计数。

一旦达到计数9(二进制1001),计数器将返回可以通过JK触发器(TTL 74LS73)制作十进制计数器的基本电路,该触发器在时钟信号的负后沿切换状态,如图所示。

0000而不是继续到1010。 MOD-10十年计数器

MOD计数器摘要

我们在本教程中看到过MOD计数器二进制计数器是由于时钟信号而产生二进制位序列的时序电路,二进制计数器的状态由所有计数器输出一起形成的特定组合决定。

计数器可以产生的不同输出状态的数量称为计数器的模数或模数。计数器的模数(或MOD数)是它在一个完整的计数周期中通过的唯一状态的总数,其中mod-n计数器也被描述为n分频计数器。

计数器的模数如下:2 n 其中n =触发器的数量。因此,3触发器计数器的最大计数为2 3 = 8个计数状态,并称为MOD-8计数器。计数器可以计算的最大二进制数是2 n -1,最大计数为(111) 2 = 2 3 - 1 = 7 10 。然后计数器从0到7计数。

通用MOD计数器包括MOD编号为2,4,8和16的计数器,并且使用外部组合电路可以配置为计数到除最大值2 n 模量。通常,“m”个触发器的任何排列都可用于构造任何MOD计数器。

具有截断序列的计数器的公共模数为10(1010),称为MOD-10。在其序列中具有十个状态的计数器被称为十进制计数器。十进制计数器对于连接数字显示器很有用。其他MOD计数器包括MOD-6或MOD-12计数器,它们在数字时钟中有应用以显示时间。

-

计数器

+关注

关注

32文章

2324浏览量

98698 -

D触发器

+关注

关注

3文章

182浏览量

49933

发布评论请先 登录

时序电路设计的计数器详解

基于Multisim的计数器设计仿真

同步计数器和异步计数器是什么 同步计数器和异步计数器的主要区别?

时序逻辑电路设计之同步计数器

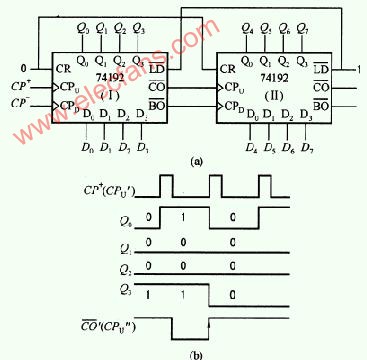

MOD计数器和时序图

MOD计数器和时序图

评论