半导体的支持工艺和CPU的性能关系就大了,它关系到CPU内能塞进多少个晶体管,还有CPU所能达到的频率还有它的功耗,1978年Intel推出了第一颗CPU——8086,它采用3μm(3000nm)工艺生产,只有29000个晶体管,工作频率也只有5MHz。

而现在晶体管数量最多的单芯片CPU应该是Intel的28核Skylake-SP Xeon处理器,它拥有超过80亿个晶体管,而频率最高的则是Core i9-9900K,最大睿频能到5GHz,他们都是用Intel的14nm工艺生产的。

Intel 14nm工艺在性能、功耗方面继续改进

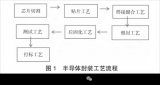

CPU的生产是需要经过7个工序的,分别是:硅提纯,切割晶圆,影印,蚀刻,重复、分层,封装,测试, 而当中的蚀刻工序是CPU生产的重要工作,也是重头技术,简单来说蚀刻就是用激光在硅晶圆制造晶体管的过程,蚀刻这个过程是由光完成的,所以用于蚀刻的光的波长就是该技术提升的关键,它影响着在硅晶圆上蚀刻的最小尺寸,也就是线宽。

现在半导体工艺上所说的多少nm工艺其实是指线宽,也就是芯片上的最基本功能单位门电路的宽度,因为实际上门电路之间连线的宽度同门电路的宽度相同,所以线宽可以描述制造工艺。缩小线宽意味着晶体管可以做得更小、更密集,而且在相同的芯片复杂程度下可使用更小的晶圆,于是成本降低了。

更先进半导体制造工艺另一个重要优点就是可以提升工作频率,缩减元件之间的间距之后,晶体管之间的电容也会降低,晶体管的开关频率也得以提升,从而整个芯片的工作频率就上去了。

另外晶体管的尺寸缩小会减低它们的内阻,所需导通电压会降低,这代表着CPU的工作电压会降低,所以我们看到每一款新CPU核心,其电压较前一代产品都有相应降低。另外CPU的动态功耗损失是与电压的平方成正比的,工作电压的降低,可使它们的功率也大幅度减小。

另外同种工艺的概率也是相当重要的,Intel自2015年14nm工艺投产以来已经发展到了第三代,Intel一直在改进工艺,在不提升功耗的情况不断提升性能,14nm++工艺比初代14nm工艺性能提升26%,或者功耗降低52%。

实际上AMD Ryzen处理器现在所用的12nm工艺本质上也只是GlobalFoundries的14nm工艺的改良版,也就是原计划的14nm+,晶体管密度并没有提升,但在性能方面有所改善,最高工作频率提升了250MHz,而同频下Vcore下降了50mV。

多年前Intel对自家半导体工艺的进展预期,此处应该有个滑稽的表情。

总的来说半导体工艺是决定各种集成电路性能、功耗的关键,线宽的缩小晶体管密度得以提升从而降低了成本,其次就是晶体管频率提高,性能提升而功耗降低。

-

处理器

+关注

关注

68文章

19461浏览量

231421 -

芯片

+关注

关注

457文章

51345浏览量

428267 -

半导体

+关注

关注

335文章

27826浏览量

223873 -

cpu

+关注

关注

68文章

10922浏览量

213283 -

晶体管

+关注

关注

77文章

9796浏览量

139070

原文标题:半导体工艺如何影响CPU性能的?

文章出处:【微信号:iawbs2016,微信公众号:宽禁带半导体技术创新联盟】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

半导体固晶工艺深度解析

半导体固晶工艺大揭秘:打造高性能芯片的关键一步

倒装封装(Flip Chip)工艺:半导体封装的璀璨明星!

半导体晶圆制造工艺流程

【「大话芯片制造」阅读体验】+跟着本书”参观“半导体工厂

一文详解半导体薄膜沉积工艺

总投资45亿元,西安8英寸高性能特色工艺半导体芯片生产线项目实现“交地即交证”

半导体发展的四个时代

半导体发展的四个时代

半导体封装工艺面临的挑战

半导体工艺如何影响CPU性能的?

半导体工艺如何影响CPU性能的?

评论