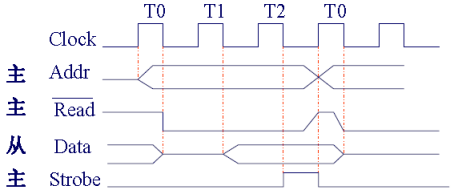

(1) 同步方式

•发送、接收双方统一步调,具备统一的时钟信号。•完全由同步时钟确定收发时刻,没有应答信号。•例:总线的读操作

(2) 异步方式

•发送、接收双方根据自身的工作速度来确定总线传送的步调•没有统一的时钟信号,有主同步MSYN和从同步SSYN

•MSYN上升沿:主设备启动输入•SSYN上升沿:从设备已将数据准备好;•MSYN下降沿:主设备已将数据取走;•SSYN下降沿:从设备让出数据总线•特点:各设备以自身需要的速度工作,时间利用率高。

·事件C: Ssyn↑→Msyn↓

·事件R: Msyn↓ → Ssyn ↓

·全互锁:有C且有R

·半互锁:或有C、或有R

(3) 准同步方式在完全同步方式中加一点异步的手段。有同步时钟,也有应答信号线。同步地采样应答信号

总线操作方式

微机系统各部件之间的信息交换是通过总线操作周期完成的,一个总线周期通常分为以下四个阶段。

① 总线请求和仲裁阶段:当有多个模块提出总线请求时,必须由仲裁机构仲裁,确定将总线的使用权分配给哪个模块。

② 寻址阶段:取得总线使用权的模块,经总线发出本次要访问的存储器或I/O端口的地址和有关命令。

③ 传送数据阶段:主模块(指取得总线控制权的模块)与其他模块之间进行数据的传送。

④ 结束阶段:主模块将有关信息从总线上撤除,主模块交出对总线的控制权。

-

FPGA

+关注

关注

1628文章

21722浏览量

602870 -

时序

+关注

关注

5文章

387浏览量

37309

原文标题:总线的操作时序和操作方式详解

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

SSH远程操作的基本方式

vim的操作方式有哪几种

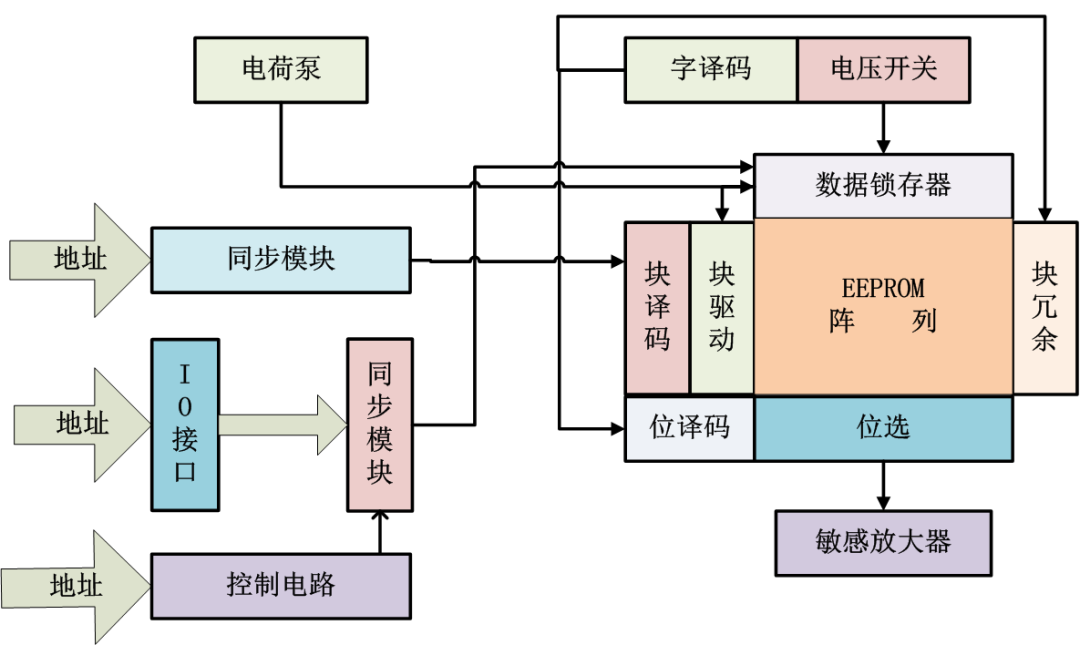

DRAM内存操作与时序解析

异步总线中传送操作的控制机制

TSMaster 中不同总线报文消息过滤的操作方式

STM32H7 FMC操作SDRAM读比写慢很多是为什么?

TSMaster 总线记录功能操作指南

GPIF II接口读操作和写操作之间间隔应该是多少?

时序电路的分类 时序电路的基本单元电路有哪些

TC275操作I2C读操作时陷入while循环无法退出怎么解决?

详解实时操作系统和非实时操作系统

冷热冲击试验机操作流程五步详解

总线的操作时序和操作方式详解

总线的操作时序和操作方式详解

评论