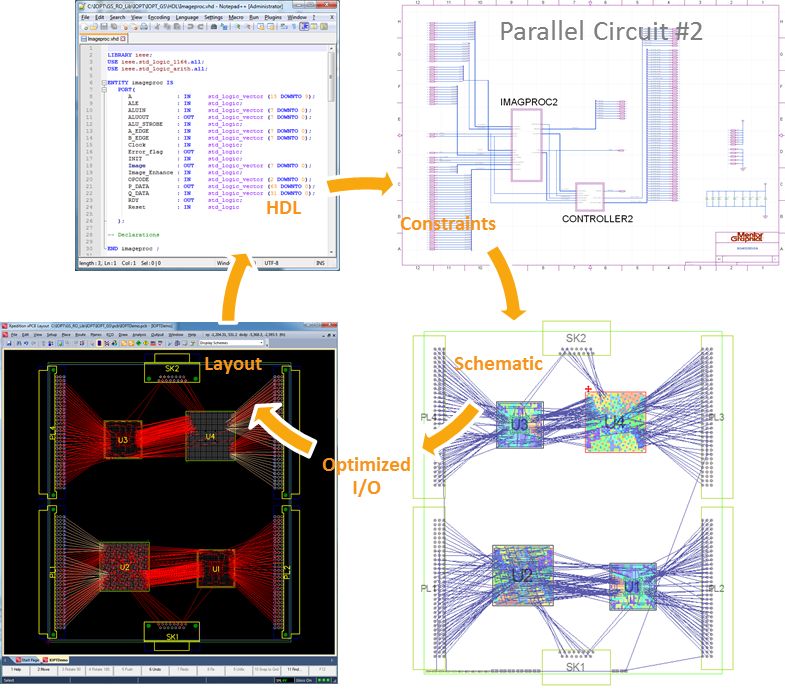

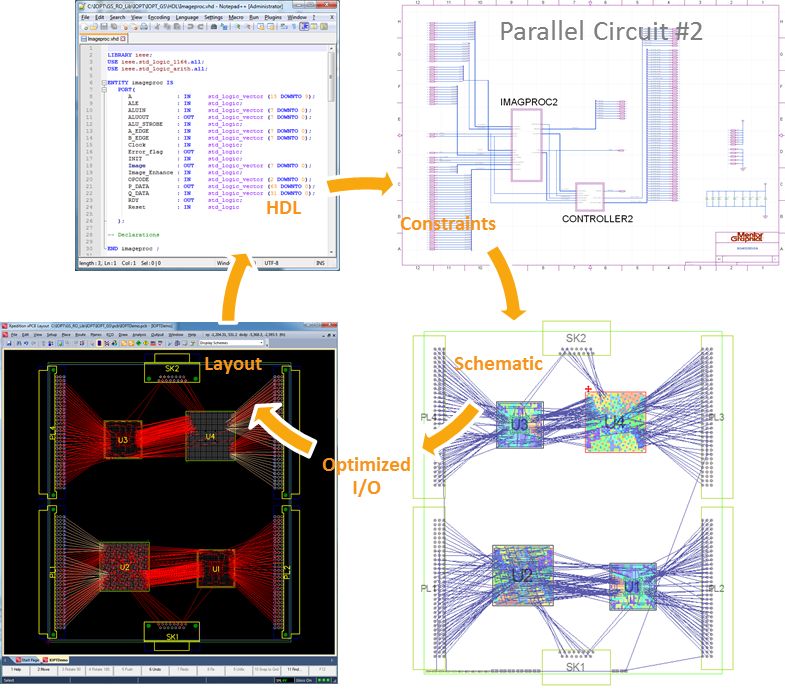

随着电子产品的集成性及复杂度呈指数型增长,加上越来越苛刻的研发周期要求,给各种设计公司提出了难题。这其中FPGA的设计挑战尤为突出。不断增加的管脚数量,同一PCB上的多颗FPGA之间互连等等,面对这些挑战如果还依照以往的手动式设计流程,势必会在激烈的市场竞争中失去优势!Mentor公司针对这种实际应用情况,提出了集成式管脚优化方案,根据信号连接关系及器件位置摆放信息,自动实现IO管脚优化,在保证产品质量的前提下,高效完成FPGA设计及优化工作,在最短的时间内使产品顺利上市!

4大技术优势:

1缩减设计成本:

减少过孔数量

节省PCB叠层数量

减少生产制造迭代次数

2缩短设计周期:

减少设计迭代次数

提升FPGA布线效率

快速优化IO管脚,自动生成器件symbol

3减少设计失误:

杜绝器件symbol设计失误

避免手动更换IO管脚而造成的失误

4提高产品质量:

减少布线长度,提升信号质量

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

原文标题:不容错过的研讨会 | 复杂FPGA高效设计及优化方法

文章出处:【微信号:gh_1a93bb3ab6f3,微信公众号:Mentor明导PADS】欢迎添加关注!文章转载请注明出处。

相关推荐

使用RISC-V进行高效数据处理的方法涉及多个方面,包括处理器内核与DSA(领域特定加速器)之间的通信优化、内存管理优化、多线程性能提升等。以下是一些具体的

![的头像]() 发表于

发表于 12-11 17:52

•373次阅读

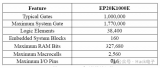

我们在比较FPGA的芯片参数时经常说某一款FPGA是多少万门的,也有的说其有多少个LE,那么二者之间有何关系呢?

FPGA等效门数的计算方法有两种,一是把

![的头像]() 发表于

发表于 11-11 09:45

•292次阅读

优化FPGA(现场可编程门阵列)设计的性能是一个复杂而多维的任务,涉及多个方面和步骤。以下是一些关键的优化策略: 一、明确性能指标 确定需求 :首先,需要明确

![的头像]() 发表于

发表于 10-25 09:23

•353次阅读

本文描述了一种简单高效配置FPGA的方法,该方法利用微处理器从串行外围接口(SPI)闪存配置FPGA设备。这种

![的头像]() 发表于

发表于 10-24 14:57

•633次阅读

AI大模型的性能优化是一个复杂而关键的任务,涉及多个方面和策略。以下是一些主要的性能优化方法: 一、模型压缩与优化 模型蒸馏(Model D

![的头像]() 发表于

发表于 10-23 15:01

•723次阅读

引言由于芯片设计复杂度的提升、集成规模的扩大,以及产品上市时间要求的缩短,使得设计验证变得更加困难。特别是在多FPGA环境中,设计调试和验证的复杂性进一步增加,传统的调试手段难以满足对高性能、

![的头像]() 发表于

发表于 10-09 08:04

•741次阅读

,FPGA 也需要不断适应和改进。研究人员和开发者将致力于针对 FPGA 的特点对深度学习算法进行优化,例如探索更高效的模型压缩方法、量化技

发表于 09-27 20:53

在FPGA(现场可编程门阵列)设计中,消除时钟抖动是一个关键任务,因为时钟抖动会直接影响系统的时序性能、稳定性和可靠性。以下将详细阐述FPGA中消除时钟抖动的多种方法,这些方法涵盖了从

![的头像]() 发表于

发表于 08-19 17:58

•1364次阅读

减少错误并更容易调试。然而,经常出现的问题是性能权衡。在高度复杂的 FPGA 设计中实现高性能需要手动优化 RTL 代码,而这对于HLS开发环境生成的 RTL 代码来说是不可能的。然而,存在一些解决方案

发表于 08-16 19:56

在FPGA(现场可编程门阵列)中实现状态机是一种常见的做法,用于控制复杂的数字系统行为。状态机能够根据当前的输入和系统状态,决定下一步的动作和新的状态。这里,我们将详细探讨如何在FPGA设计中实现状态机,包括其基本概念、类型、设

![的头像]() 发表于

发表于 07-18 15:57

•614次阅读

FPGA(现场可编程门阵列)在处理异步信号时,需要特别关注信号的同步化、稳定性以及潜在的亚稳态问题。由于异步信号可能来自不同的时钟域或外部设备,其到达时间和频率可能不受FPGA内部时钟控制,因此处理起来相对复杂。以下是对

![的头像]() 发表于

发表于 07-17 11:10

•1173次阅读

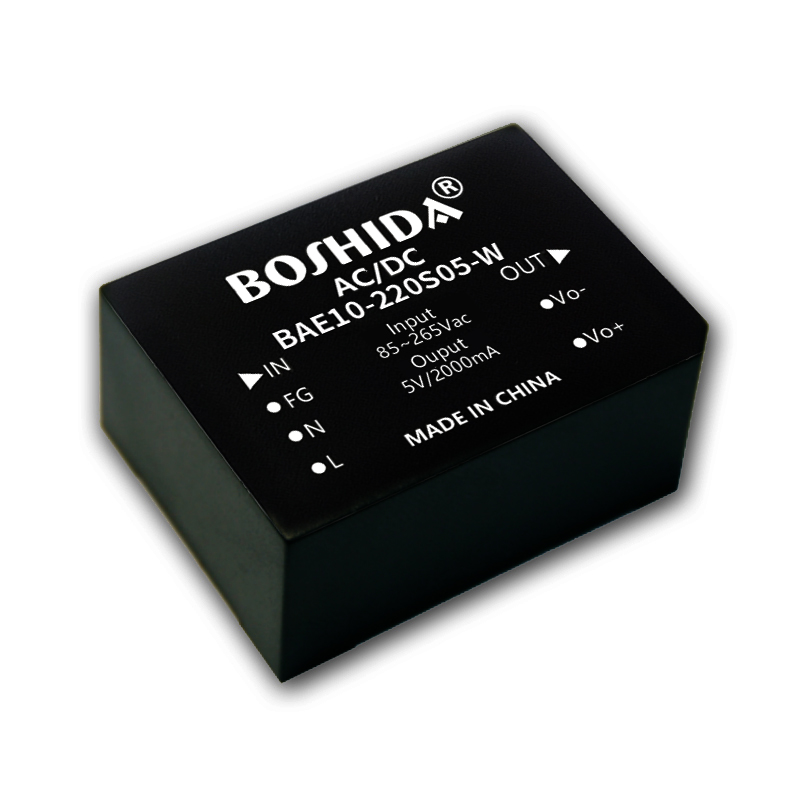

BOSHIDA AC/DC电源模块的高效能源管理与效率优化 AC/DC电源模块是一种常见的电源转换装置,用于将交流电转换为直流电。它被广泛应用于各种电子设备中,如计算机、通信设备、工业自动化设备等

![的头像]() 发表于

发表于 05-06 13:31

•315次阅读

这种高带宽的互联做了设计和优化,更是在FPGA上集成了NOC,跟传统FPGA中的routing有很大的区别,这也让我们在复杂设计中可以减少因为Congestion导致的各种问题,减少代

发表于 04-24 15:09

功能,从而实现对数字电路的高效定制。FPGA语言主要包括VHDL(VHSIC Hardware Description Language)和Verilog等,这些语言具有强大的描述能力,能够精确地定义硬件的每一个细节,从而实现复杂

![的头像]() 发表于

发表于 03-15 14:50

•949次阅读

成本具有重要意义。

设计优化:书中对FPGA加速器的技术进行了优化,例如循环平铺和转换,并通过定量分析计算吞吐量和片内外I/O带宽,帮助读者理解如何设计出更高效的加速器硬件参数。

实际

发表于 01-31 21:14

复杂FPGA高效设计及优化方法

复杂FPGA高效设计及优化方法

评论