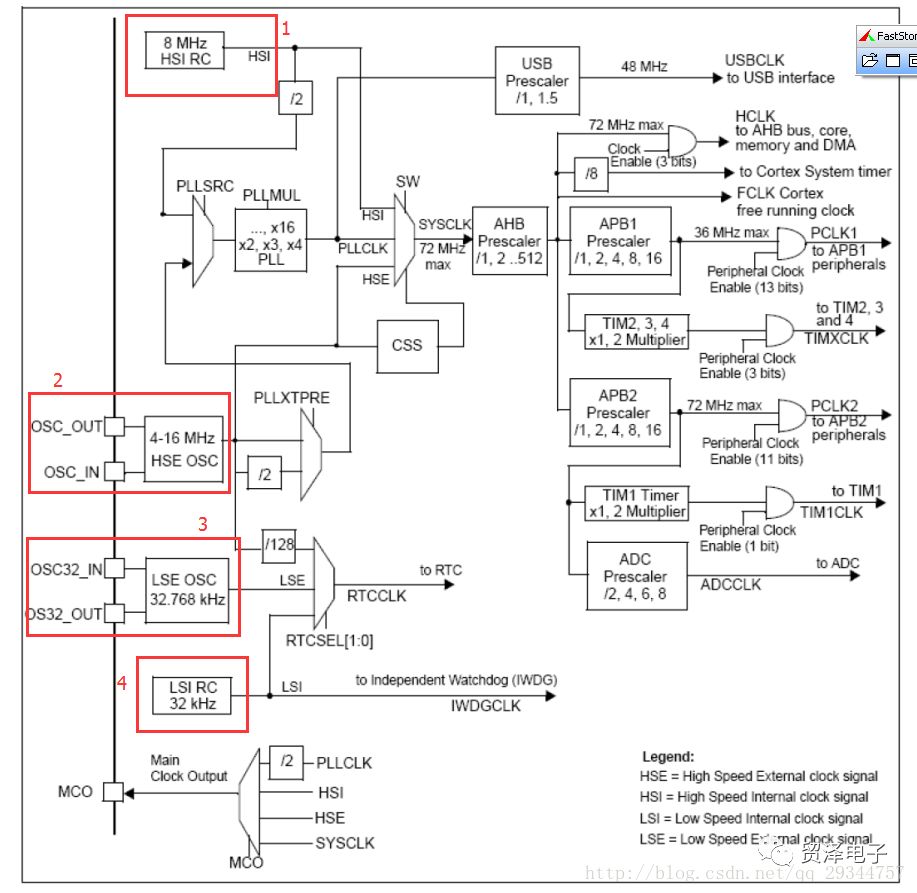

STM32的时钟体系可以直接以图概括(摘自STM32F10X参考手册)

下面就此图做分析

1. STM32输入时钟源

1.1 时钟源的作用

无论是小型单片机还是像STM32这样高级单片机,它们工作的核心都是大规模的时序逻辑电路,而驱动时序逻辑电路的关键则是准确而又稳定的时钟源。它的作用就像小学在操场上做广播体操时候播放的背景音乐,用于协调和同步各单元运行,为时序电路提供基本的脉冲信号。

1.2 STM32时钟源的设计

在51单片机中,一般都外接一个11.0592MHz的晶振,注意,提供时钟的不是晶振,而是RC时钟电路,而晶振只是时钟电路的元件之一。同理,在STM32中,时钟源也是由RC时钟电路产生,与51单片机的区别是区别在于,RC电路的位置。根据RC电路的位置,可以将STM32的时钟源分为内部时钟电路和外部时钟、内外部时钟电路。

(1)内部时钟电路:

晶体振荡器和RC时钟电路都在STM32芯片内部,如图中标注1、标注4。

标注1处是产生8MHz的时钟源,称为HSI,高速内部时钟源(H意为高速,S意为源,I意为内部);

标注4处是产生32KHz的时钟源,称为LSI,低速内部时钟源;

(2)内外部时钟电路:

晶体振荡器在STM32芯片外部,RC时钟电路在STM32芯片内部,如图中标注2、标注3。

标注2处是产生4-16MHz的时钟源,称为HSE,高速外部时钟源;

标注3是产生32.768KHz的时钟源,称为LSE,低速外部时钟源;

OSC_OUT和OSC_IN、OSC32_OUT和OS32_IN分别接晶振的两个引脚。前者一般接8MHz晶振;后者一定接32.768KHz,因为这个时钟源是供给RTC实时时钟使用的。在51单片机中没有集成RTC模块,在做电子时钟时用到的DS1302集成芯片时,也是为其提供的也是32.768KHz的晶振。

(3)外部时钟电路

晶体振荡电路和RC时钟电路都在STM32芯片外部。如图中标注2、标注3。

OSC_OUT和OSC_IN、OSC32_OUT和OS32_IN除了分别接晶振的两个引脚,对于OSC_IN和OSC32_IN引脚,还可以接入外部的RC时钟电路,其时钟源直接由外部供给,不过这种方案少见。

综上所述,STM32的时钟源有4个: HSI、HSE和LSI、LSE。

HSI时钟源,它是在由STM32在内部用RC振荡电路实现的高速内部时钟源。HIS RC振荡器能够在不需要任何外部期间的条件下提供系统时钟,它的启动时间比HSE晶体振荡器短,但是不精准,即使在校准之后它的时钟频率精度仍较差。在手册中还明确说,当HSI被用作PLL时钟输入时,系统时钟能得到的最大频率是61MHz,这显然不能发挥STM32最极致的性能。

1.3 时钟信号通道选择

虽然HSI不精准,但是鉴于启动速度原因考虑,STM32上电复位,默认是采用HSI时钟源的,当然开发者可以不修改这个时钟源,那么系统将一直工作在一个时钟源不稳定不精准的环境下。

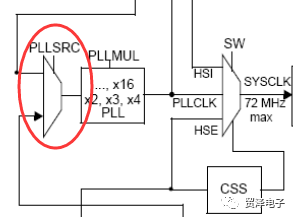

然而一般做法是改变时钟源,将时钟源改为HSE。改变时钟源的通道是在相关寄存器设置的,在图中的PLLSRC可以实现对这两个频率的切换。

1.4 锁相环倍频器PLL/预分频器Prescaler

STM32的cpu的工作常规频率是72MHZ(超过72MHz工作称为超频工作,CPU耗电加剧,且会发烫),但是我们接入的晶振是8MHz,这就需要一个对频率加倍的操作,即倍频。如图中的PLLMUL,PLLMULL实现对接入时钟源的倍频,如x2、x3、x4…倍频后的时钟源为PLLCLK。

预分频器是实现对频率削减作用的。倍频器将HSE倍频之后提供给cpu,但是除了cpu之外,其他片内外设,如SPI控制模块、IIC控制模块等的工作同样需要时钟源,这些外设的时钟源肯定是低于cpu运行时钟的,例如USB通讯才需要48MHz,所以需要对倍频后的时钟源进行分频。一般芯片的分频做法都是对一个时钟源倍频后供给某些部件,其他低于此倍频后的时钟都是基于此时钟源来分频的。用户可通过多个预分频器配置AHB,高速APB(APB2)和低速APB(APB1)域的频率。AHB和APB2域的最大频率是72MHz。APB1域的最大允许频率是36MHz。SDIO接口的时钟频率固定在HCLK / 2。

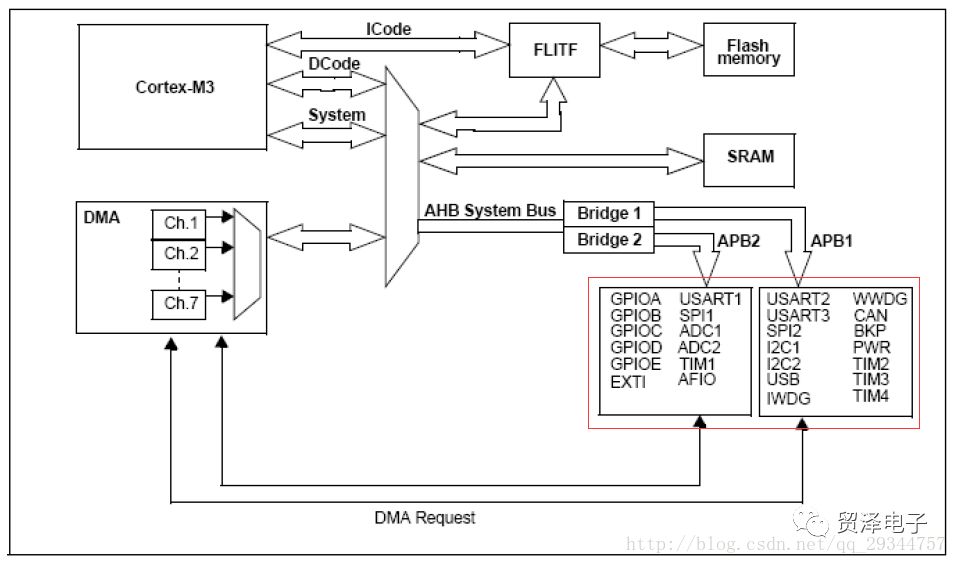

经过时钟源的选择、分频/倍频,就可以到HCLK(高性能总线AHB用)、FCLK(供给cpu内核的用,常说的cpu主频)、PCLK(高性能外设总线APB)、USBCLK、TIMXCLK、TIM1CLK、RTCCLK等,外设是挂载STM32的总线上的,具体哪个外设挂载哪个总线,看下图:

在软件开发中,我们要做的也无非设置门电路以选择时钟源输入、倍频/分频系数和打开/关闭对应外设所在总线的时钟。

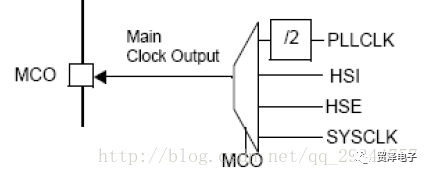

2. STM32输出时钟源

图中的MCO功能模块,可以将PLLCLK / 2、HSI、HSE、SYSCLK输出,供给其他系统作为输入时钟源,对这一功能模块也是又相应的寄存器,图中以MCO标注。

3. 系统滴答Systick

Systick就是一个定时器而已,只是它放在了NVIC中,主要的目的是为了给操作系统提供一个硬件上的中断,称之为滴答中断操作系统进行运转的时候,也会有时间节拍。它会根据节拍来工作,把整个时间段分成很多小小的时间片,而每个任务每次只能运行一个时间片的时间长度,超时就退出给别的任务运行,这样可以确保任何一个任务都不会霸占操作系统提供的各种定时功能,都与这个滴答定时器有关。因此,需要一个定时器来产生周期性的中断,而且最好还让用户程序不能随意访问它的寄存器,以维持操作系统的节拍。只要不把它在SysTick控制及状态寄存器中的使能位清除,就一直执行。

RCC(复位与时钟控制器)通过AHB时钟(HCLK)8分频后作为Cortex系统定时器(SysTick)的外部时钟。通过对SysTick控制与状态寄存器的设置,可选择上述时钟或Cortex(HCLK)时钟作为SysTick时钟(后者图中没画出)。另外,还有其他时钟,如USB时钟,ADC时钟、独立看门狗时钟等,它们各自的时钟源通过前面学习,也可以轻易分析出来,这里不再赘述。

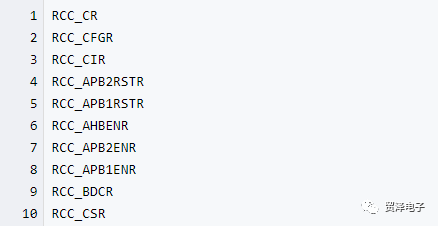

4. 时钟相关的寄存器

时钟体系涉及到的寄存器有:

-

电路

+关注

关注

172文章

5936浏览量

172484 -

寄存器

+关注

关注

31文章

5357浏览量

120668 -

时钟

+关注

关注

11文章

1736浏览量

131584

发布评论请先 登录

相关推荐

S3C2440时钟体系结构

时钟体系疑问

PSoC 5体系结构中是否存在时钟锁定?

为什么要了解时钟体系呢

Arm的DRTM体系结构规范

LTE体系结构

网络体系结构,什么是网络体系结构

体系结构建模工具SA分析

软件体系结构的分析

详解STM32时钟体系结构分析

详解STM32时钟体系结构分析

评论