在有多个供电电源的系统中,运算放大器电源必须在施加输入信号的同时或之前建立。否则,便可能发生过压和闩锁状况。

然而,在实际应用中,这个要求有时候可能难以满足。本文讨论运算放大器在不同上电时序情况下的行为表现(参见表2),分析可能的问题及原因,并提出一些建议。

上电时序问题多种多样

上电时序问题可能出现于多种不同情况。例如,在一个客户应用中,AD8616配置为缓冲器,在电源建立之前输入为0 V(图1),负电源先于正电源上电(负电源有而正电源无)。

图1. AD8616测试电路,施加–3 V V–,V+没有连接电源

表1显示了这种情况下AD8616所有引脚的结果。在正电源管脚V+上的信号建立之前,V+引脚和OUT引脚上的电压为负值。这可能不会损害运算放大器,但若这些信号连接到其他尚未完全供电的芯片上的引脚(例如,假设ADC使用同一V+,其电源引脚一般只能承受最小–0.3 V电压),则这些芯片可能会受损。如果V+先于V–上电,会发生同样的问题。

表2列出了上电时序的一些可能情况。

表1. 施加–3 V V–而V+没有连接电源时的AD8616引脚电压

| 引脚1: OUTA | 引脚2: –INA | 引脚3: +INA | 引脚4: V– | 引脚5: +INB | 引脚6: –INB | 引脚7: OUTB | 引脚8: V+ |

| –1.627 | –1.627 | –0.959 | –3.000 | –0.959 | –1.627 | –1.627 | –1.627 |

表2. 上电时序的可能情况IN

| IN | V+ | V– | 放大器电源有其他负载 | 放大器输出有负载 | |

| 情形 1 |

浮空 浮空 |

有 无 |

无 有 |

否 否 |

否 否 |

| 情形 2 |

0 V 0 V |

有 无 |

无 有 |

否 否 |

否 否 |

| 情形 3 |

正或负 正或负 |

有 无 |

无 有 |

否 否 |

否 否 |

| 情形 4 |

正或负 正或负 正或负 正或负 |

有 有 无 无 |

无 无 有 有 |

是 否 是 否 |

否 是 否 是 |

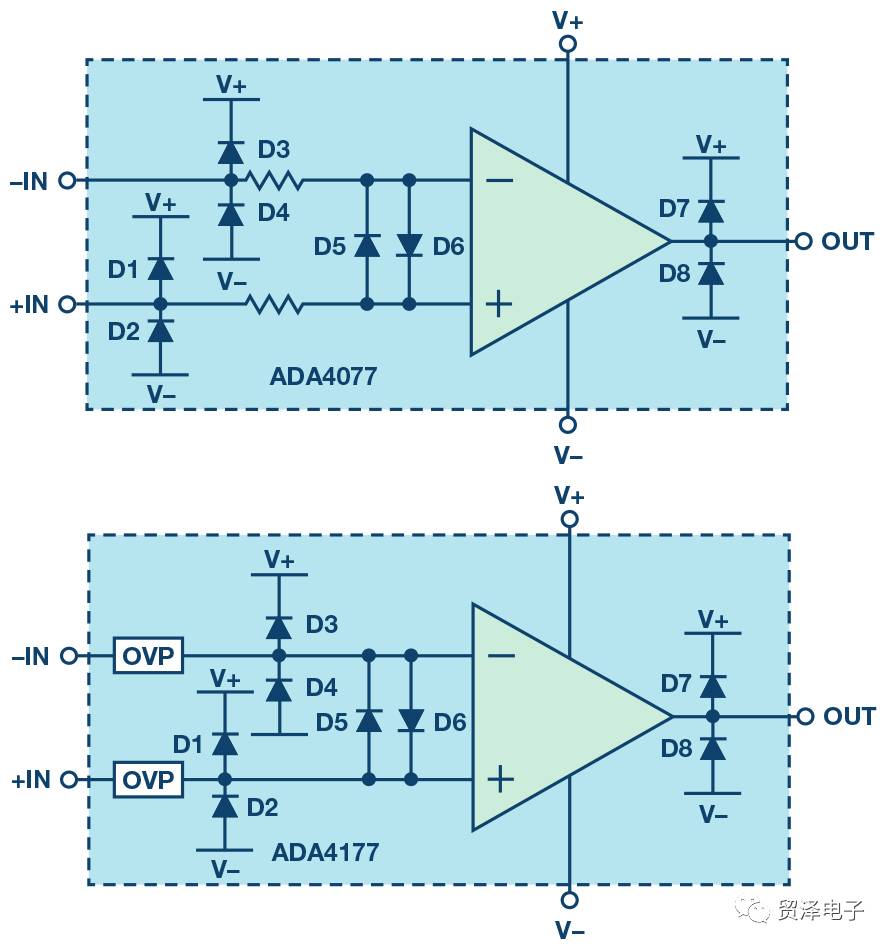

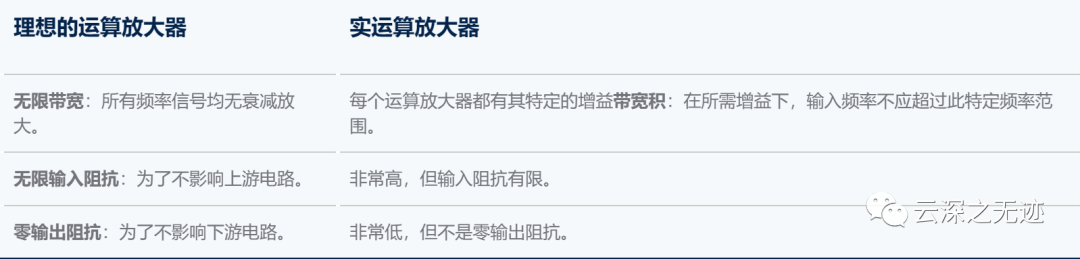

静电放电可能引起过压事件。大部分运算放大器内置ESD二极管 以防止静电ESD事件。当V+或V–不存在时,ESD二极管是分析放大 器相关行为的重要工具。图2为ADA4077/ADA4177的简化框图。表3 显示了ADA4077-2/ADA4177-2内部ESD二极管和背靠背二极管的典 型压降。注意,背靠背二极管位于运算放大器的两个输入引脚之间, 用来箝位放大器允许输入的最大差分信号。

图2. ADA4077/ADA4177简化框图

表3. 运算放大器内部二极管

| ADA4077 | ADA4177 | |

| D1 | 0.838 | 未知 |

| D2 | 0.845 | 未知 |

| D3 | 0.837 | 未知 |

| D4 | 0.844 | 未知 |

| D5 | 未知 | 未知 |

| D6 | 未知 | 未知 |

| D7 | 0.841 | 0.849 |

| D8 | 0.842 | 0.849 |

还要注意,当利用DMM测量ADA4077-2的D5/D6时,结果显示两个输 入引脚之间无二极管。事实上,背靠背二极管之前有两个串联电阻, 用来将输入电流限制在±10 mA以下。内部电阻和背靠背二极管将 差分输入电压限制在±Vs,以防止基极-发射极结点击穿。

A DA4177集成了OVP单元以提高鲁棒性。它们位于ESD二极管和 背靠背二极管之前,因此很难用DMM测量这些二极管的管压降。 ADA4177的输出ESD二极管的管压降是可以测量的。

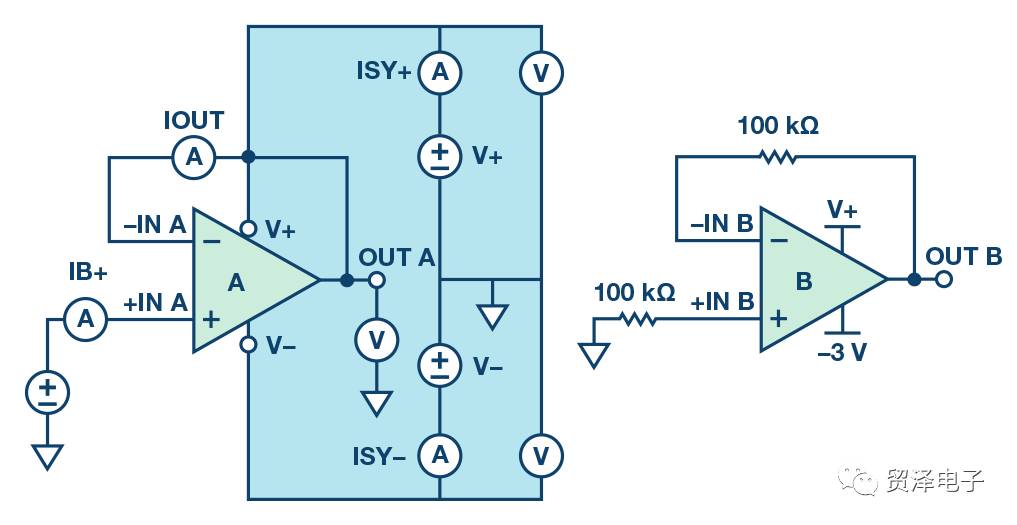

建立评估系统

图3用于测量运算放大器电路的电流流向等行为。通道A和通道B各 自配置为缓冲器,通道B同相输入端经由100 kΩ电阻连接到GND。让 V+不供电(V–供电)或V+供电(V–不供电),便可利用安培表和电 压表测量输入及电源相关变量(电压值和电流值)。通过分析这些 变量,可以确定电流流动的路径。

图3. 放大器电流路径评估系统建立

情形1:输入悬空

表4显示了一个输入悬空和一个电源未供电时的结果。当V–供电而 V+不供电时,V+引脚上有一个负电压。当V+供电而V–不供电时,V– 引脚上有一个正电压。

测试ADA4077-2和ADA4177-2得到类似的结果。输入引脚和电源引 脚上没有观测到大电流,输入悬空的运算放大器在一个供电轨没 有供电时仍然是安全的。

情形2:输入接地

表5显示了输入接地时的结果。注意,对于IB+,负值意味着电流流 出+IN引脚。对于IOUT,负值意味着电流流出–IN引脚。

表4. ADA4077-2/ADA4177-2输入悬空时的结果

| 条件 | V+ | V– | ISY+ (mA) | ISY– (mA) | IB+ (mA) | IOUT (mA) | IN (V) | OUT (V) | |

| ADA4077-2 | 正负电源都上电 | 15 | –15 | 1.02 | 1.01 | –0.00005 | 0.00007 | 0.001 | –0.008 |

| V+ 无 | –13.1 | –15 | 0 | 0.12 | –0.00001 | 0.001 | –13.73 | –14.42 | |

| V– 无 | 15 | 13.06 | 0.15 | 0 | –0.00001 | 0.001 | 12.93 | 13.62 | |

| ADA4177-2 | 正负电源都上电 | 15 | –15 | 0.98 | 0.96 | –0.00001 | 0.00002 | 0 | 0.001 |

| V+ 无 | –14.26 | –15 | 0 | 0.14 | –0.00002 | 0.00137 | –13.77 | –13.78 | |

| V– 无 | 15 | 12.96 | 0.14 | 0 | –0.00001 | –0.00039 | 12.26 | 12.31 |

表5. ADA4077-2/ADA4177-2输入接地时的结果

| 条件 | V+ | V– | ISY+&(mA) | ISY– (mA) | IB+ (mA) | IOUT (mA) | IN (V) | OUT (V) | |

| ADA4077-2 | 正负电源都上电 | 15 | –15 | 1.01 | 1 | –0.00005 | 0.00001 | 0 | –0.019 |

| V+ 无 | –0.846 | –15 | 0 | 2.30 | 2.300 | –1.60 | –0.017 | –2.68 | |

| V– 无 | 15 | 0.847 | 1.78 | 0 | –1.758 | 1.064 | 0.12 | 2.116 | |

| ADA4177-2 | 正负电源都上电 | 15 | –15 | 0.98 | 0.96 | –0.00001 | 0.00002 | 0 | 0 |

| V+ 无 | –11.99 | –15 | 0 | 9.3 | 9.300 | –0.200 | –0.068 | –11.98 | |

| V– 无 | 15 | 1.848 | 1.84 | 0 | –1.823 | 0.067 | 0.013 | 1.851 |

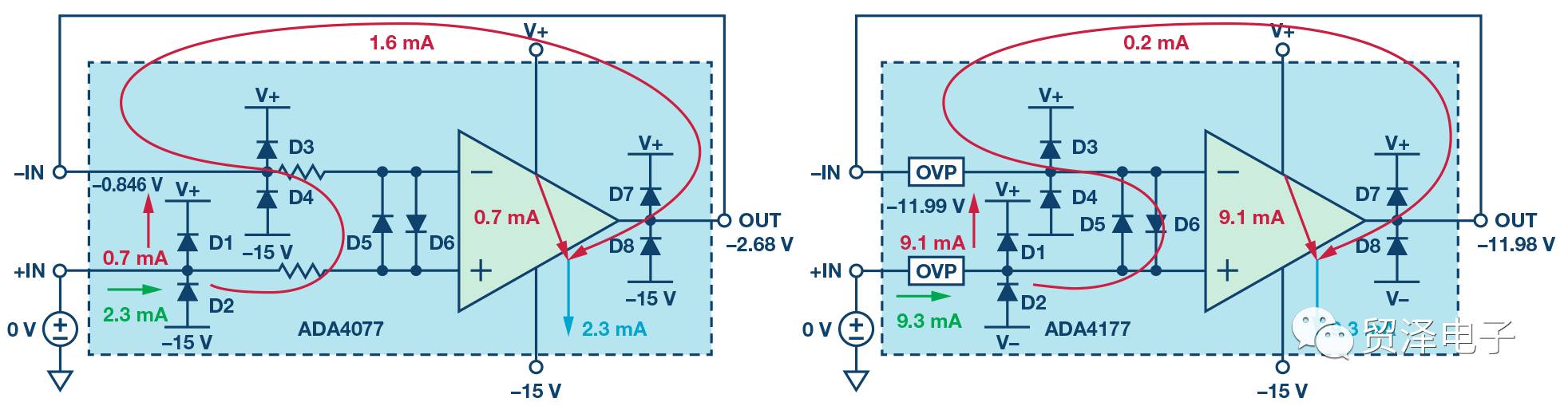

以ADA4077-2 V+未上电的情况为例,ESD二极管将V+箝位于VIN电压。

V I N通过E S D箝位二极管连接到V+,因此当V I N为0 V时,V+ 为–0.846 V。

电流流动路径:如图4中的红色路径所示,0.7 mA电流从GND (+IN)流到V+。1.6 mA电流从GND (+IN)经过内部电阻、D5以及–IN 和OUT之间的反馈路径,流入输出端。最后,这两个电流(0.7 mA 和1.6 mA)汇合流至–15 V,合并后的电流流回GND (+IN)。

ADA4177-2和ADA4077-2的结果类似。注意,ADA4177-2中的D1是通 过横向PNP晶体管的发射极基极实现的。该晶体管将过压电流从V+ 带走到V–。图4中的ADA4177电路显示有9.1 mA电流从V+流回V–,并 与反馈路径中的0.2 mA电流汇合,产生9.3 mA电流流至–15 V,然后 该电流流回GND。

ADA4077-2或ADA4177-2的输入引脚和电源引脚均未观测到大电流(表 5)。增益为+1且+IN接地时,这些运算放大器可承受任何时序的PU上电。

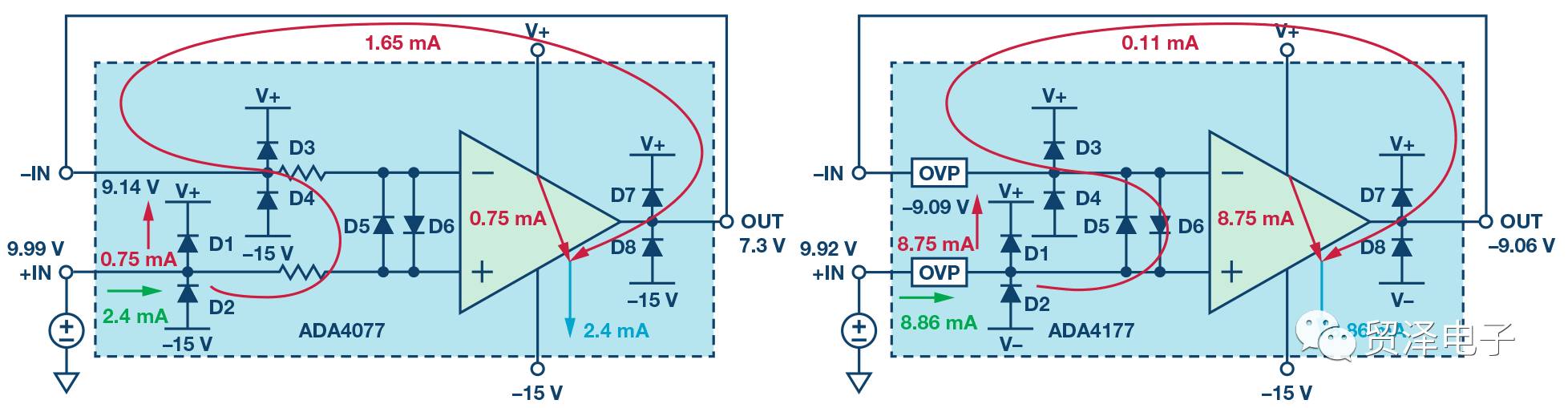

情形3:有输入

在一个电源未上电的情况下,将一个正信号或负信号(+10 V或-10 V) 施加于+IN端。表6显示没有大电流,因此当增益为+1且+IN有输入时, 这些运算放大器可承受任何顺序的PU上电。

电流流动路径分析与情形2(0 V输入)相似,参见图5。

图4. V+未上电时ADA4077/ADA4177电流路径(输入接地)

图5. V+未上电时ADA4077/ADA4177电流路径(10 V输入)

表6

| 条件 | V+ | V– | ISY+ (mA) | ISY– (mA) | IB+ (mA) | IOUT (mA) | IN (V) | OUT (V) | |

| ADA4077-2 | 正负电源均上电 | 15 | –15 | 1.03 | 1.01 | 0.00098 | –0.00003 | 10 | 9.97 |

| V + 不存在,正输入 | 9.14 | –15 | 0 | 2.4 | 2.396 | –1.653 | 9.99 | 7.3 | |

| V + 不存在,负输入 | –10.83 | –15 | 0 | 2.41 | 2.308 | –1.651 | –10.02 | –12.66 | |

| V – 不存在,正输入 | 15 | 10.83 | 1.81 | 0 | –1.689 | 1.055 | 10.02 | 12.09 | |

| V– 不存在,负输入 | 15 | –9.15 | 1.77 | 0 | –1.759 | 1.031 | –9.99 | –7.88 | |

| ADA4177-2 | 正负电源均上电 | 15 | –15 | 1.02 | 1 | –0.00099 | –0.00009 | 9.99 | 9.97 |

| V+ 不存在,正输入 | –9.09 | –15 | 0 | 8.86 | 8.866 | –0.113 | 9.92 | –9.06 | |

| V+ 不存在,负输入 | –12.33 | –15 | 0 | 4.31 | 4.18 | –0.039 | –10.02 | –12.32 | |

| V– 不存在,正输入 | 15 | 11.42 | 1.33 | 0 | –1.2 | 0.056 | 9.99 | 11.43 | |

| V– 不存在,负输入 | 15 | –8.33 | 1.51 | 0 | –1.492 | 0.062 | –9.97 | –8.32 |

情形4:有输入且电源/输出有负载

在实际应用中,运算放大器电路可能要与其他电路一起工作。例如, 运算放大器的输出可能会驱动一个负载,或者运算放大器的电源 会为其他电路供电。这会引起问题。

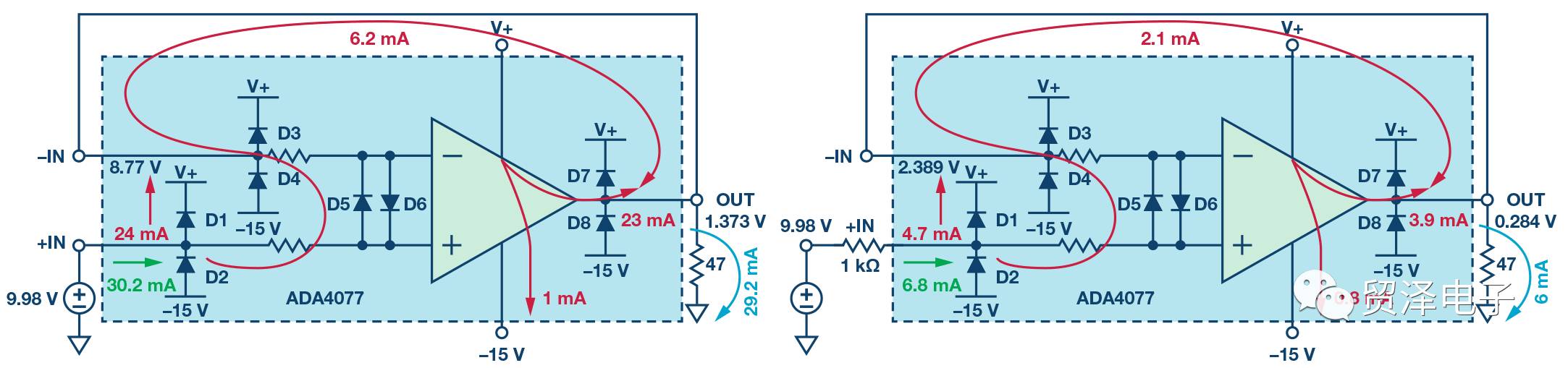

在该测试中,一个47 Ω电阻连接在输出与GND之间,或连接在未上 电的电源引脚与GND之间。图7显示了ADA4077的测试结果。三种可 能情况会带来风险(假定V+未上电):

情况1:当输入为10 V且OUT负载为47 Ω时,输出为1.373 V。有23 mA电流从运算放大器的输出引脚流出(参见图6),电流路径为:

输入信号源提供30.2 mA电流

24 mA电流流经D1至V+,6.2 mA电流流经D5和反馈路径至OUT

来自V+的24 mA电流分为1 mA(至V–)和23 mA(至OUT)

29.2 mA电流流经47 Ω负载至GND

ADA4077-2允许的输入电流最大为10mA,所以需要限流。在+IN端 增加一个1 kΩ电阻,可使输入电流降至6.8 mA。

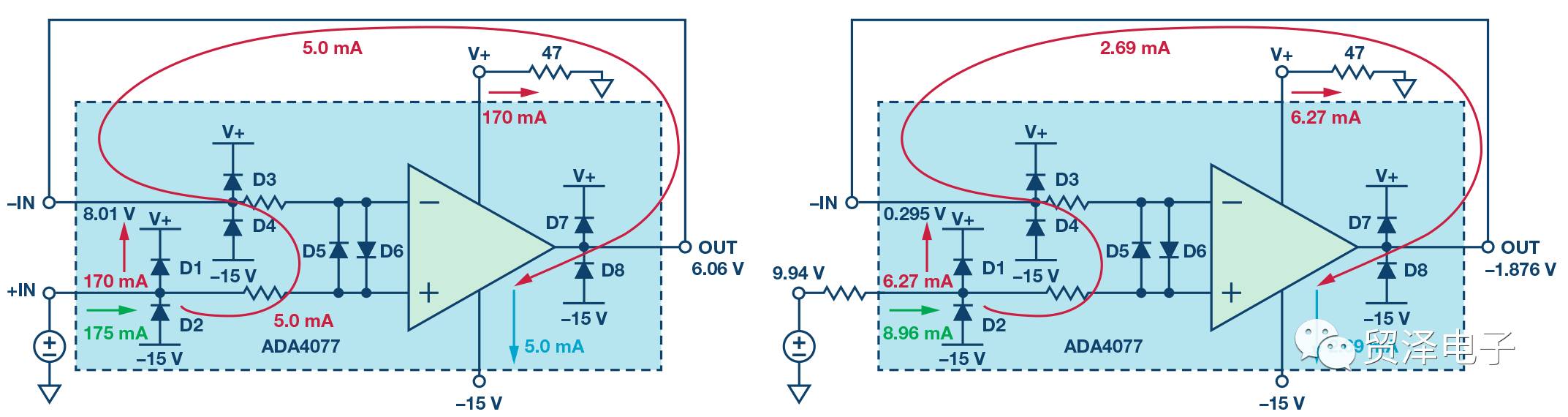

情况2:当输入为10 V且V+负载为47 Ω时,170 mA电流会流入 ADA4077-2,并从V+引脚流出到47 Ω电源负载。170 mA电流会烧 毁内部二极管,损坏芯片。在+IN端增加一个1 kΩ电阻,可使输入 电流降至8.9 mA。图7显示了电流流动路径。

表7.ADA4077的输出引脚或无电源的电源引脚上有负载

| ADA4077-2 | 条件 | IN (V) | V+ | V– | ISY+ (mA) | ISY– (mA) | IB+ (mA) | IOUT (mA) | OUT (V) |

| V+ 无 | Vo 或 V+ 无负载/正输入 | 9.99 | 9.14 | –15 | 0 | 2.4 | 2.396 | –1.653 | 7.3 |

| Vo 47 Ω 至 GND | 9.98 | 8.77 | –15 | 0 | 1.00 | 30.22 | –6.174 | 1.373 | |

| Vo 47 Ω 至 GND 和 1 kΩ | 9.98 | 2.389 | –15 | 0 | 0.76 | 6.828 | –2.104 | 0.284 | |

| V+ 47 Ω 至 GND | 9.59 | 8.01 | –15 | 170 | 5.05 | 175 | –5.0 | 6.06 | |

| V+ 47 Ω 至 GND 和 1 kΩ | 9.94 | 0.295 | –15 | 6.27 | 2.69 | 8.96 | –2.69 | –1.876 | |

| Vo 或 V+ 无负载/负输出 | –10.02 | –10.83 | –15 | 0 | 2.41 | 2.308 | –1.651 | –12.66 | |

| Vo 47 Ω 至 GND | –9.97 | –3.226 | –15 | 0 | 48.6 | –4.65 | 4.885 | –2.501 | |

| Vo 47 Ω 至 GND 和 1 kΩ | –10.02 | –10.83 | –15 | 0 | 14.30 | 2.284 | –1.629 | –0.563 |

图6. V+未上电时ADA4077的电流路径(10 V输入和47 Ω输出负载)

图7. V+未上电时ADA4077的电流路径(10 V输入和47 Ω电源负载)

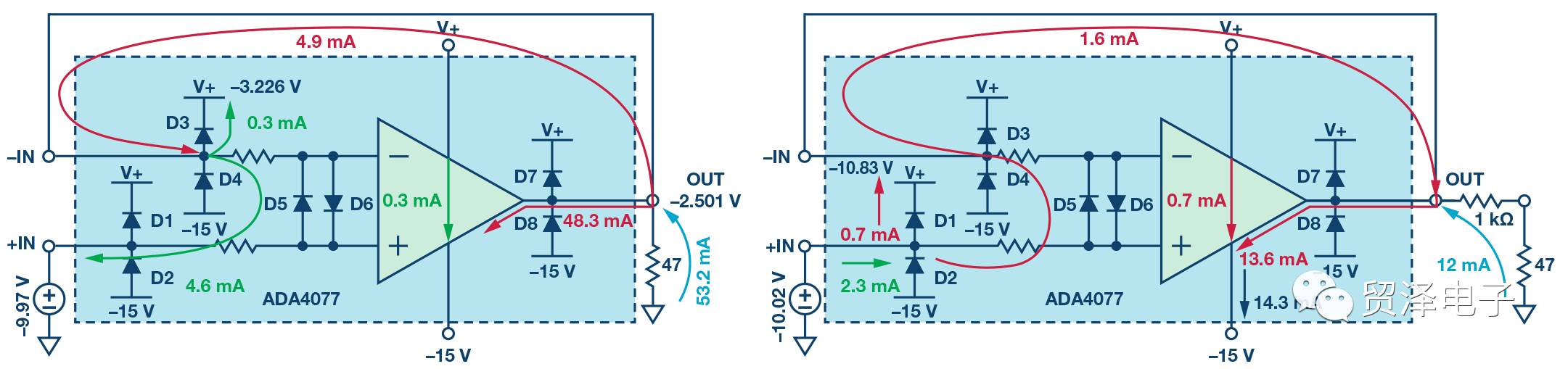

情况3:当输入为负(-10 V)且OUT负载为47 Ω时(参见图8),有48 mA电流流经芯片。由此产生的功耗为48 mA × (–2.5 V + 15 V) = 0.6 W。ADA4077-2的θJA为158°C/W,因此结温比环境温度高出 94.8°。若有两个通道或负载更重,结温可能高于150°,致使芯片 受损。

不应在输入端增加限流电阻,而应在输出端增加限流电阻。

当V+上电而V–未上电时,会发生同样的现象。通过增加外部电 阻来限制电流,电路鲁棒性可以变得更好。

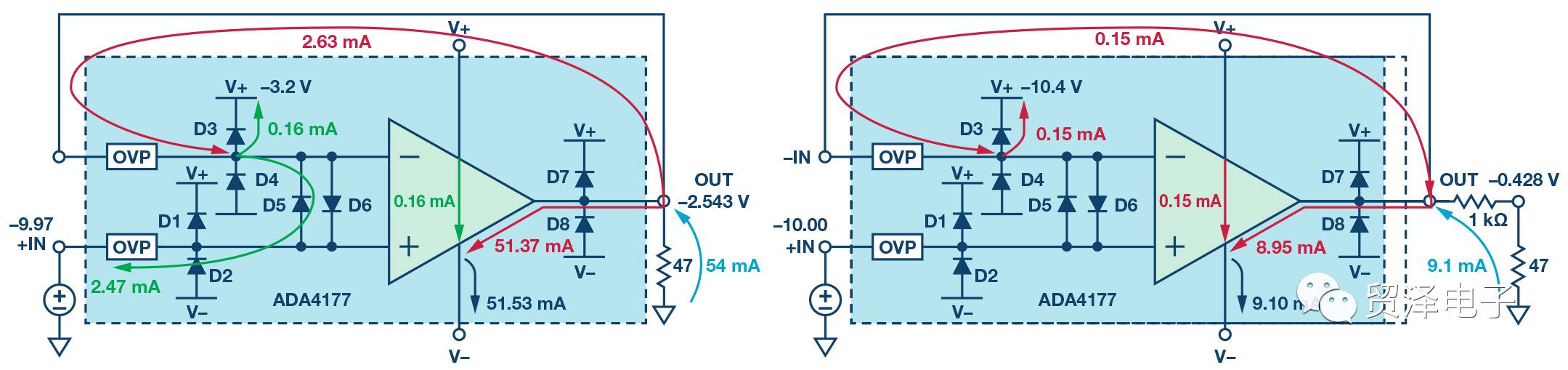

对于ADA4177-2,仅情况3适用。当有很大的负输入,同时输出端有 很重的负载,且V+未上电时,有53 mA电流流经芯片,功耗可能会 增加,结温随之提高(参见图9)。通过在输出端增加一个1 kΩ电阻, 可以避免这种风险。

在这两款运算放大器中,ADA4177-2比ADA4077-2更鲁棒。在同时要 求高精度和鲁棒性的应用中,前者是不错的选择。

其他运算放大器在不同上电时序下的表现

在运算放大器内部,二极管、电阻和OVP单元有各种各样的实施方式。 有些运算放大器没有内部OVP单元,有些没有背靠背二极管,有些没 有内部限流电阻。如果一个电源未上电,放大器不同的内部结构会产 生不同的结果。此外,不同的运算放大器设计也会产生不同的结果。

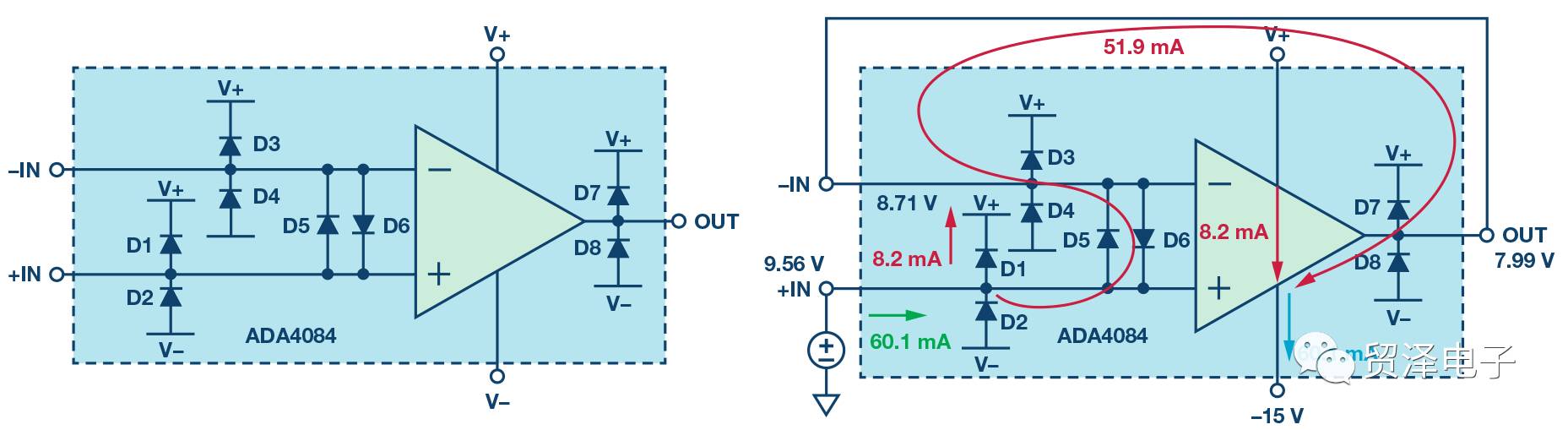

例如,ADA4084-2没有内部限流电阻和OVP单元,其ESD二极管连接 到电源和背靠背二极管。表9和图10显示了V+未上电且有10 V输入 时的结果。ADA4084的电流路径与ADA4077-2和ADA4177-2相似(上 文中的情形3已讨论)。然而,ADA4084没有内部电阻或OVP单元来 限制电流,60 mA电流会流入芯片,可能引起损害。

图8. V+未上电时ADA4077的电流路径(-10 V输入和47 Ω输出负载)

图9. V+未上电时ADA4177的电流路径(-10 V输入和47 Ω输出负载)

图10. V+未上电时ADA4084的电流路径(10 V输入)

表8. ADA4177的输出引脚或无电源的电源引脚上有负载

| ADA4177-2 | 条件 | IN (V) | V+ | V– | ISY+ (mA) | ISY– (mA) | IB+ (mA) | IOUT (mA) | OUT (V) |

| V+ 无 | Vo 或 V+ 浮空和负输入 | –10.02 | –12.33 | –15 | 0 | 4.31 | 4.18 | –0.039 | –12.32 |

| Vo 47 Ω 至 GND | –9.97 | –3.218 | –15 | 0 | 51.53 | –2.473 | 2.632 | –2.543 | |

| Vo 47 Ω 至 GND 和 1 kΩ | –10 | –10.4 | –15 | 0 | 9.10 | –0.003 | 0.147 | –0.428 | |

表9

| ADA4084-2 | Condition | V+ | V– | I+(mA) | I– (mA) | IB+ (mA) | IOUT (mA) | IN (V) | OUT (V) |

| 正负电源均上电 | 15 | –15 | 1.38 | 1.37 | –0.001 | –0.0001 | 10 | 9.98 | |

| V+ 未上电,正输入 | 8.71 | –15 | 0 | 60.1 | 60.102 | –51.89 | 9.56 | 7.99 | |

在系统应用中,不同的运算放大器、不同的拓扑结构(如同相放大、 反相放大、差动放大等)、不同的负载和外部连接都可能存在。如 果存在有某个电源未上电的情况,需要对风险进行评估。本文介绍 了如何搭建评估风险的电路(图2)、如何分析电流路径以及评估潜 在的风险。

总结

为了避免过压或闩锁情况,必须同时建立运算放大器电源。一般指 南如下:

上电时,先接通电源,再在输入端施加信号

关断时,先关闭输入信号,再关闭电源

在实际应用中,可能难以遵守这些指导原则。这可能会引起问题, 尤其是当有输入信号时,设计人员需要适当评估风险。一种有效的 解决方案是限制运算放大器的输入电流,使它在数据手册给出的 规格以内。在无法同时上电的应用中,输入端和输出端增加限流电 阻会有帮助。

我们在电源未上电的应用中测试了三款ADI运算放大器(ADA4084-2、 ADA4077-2和ADA4177-2)。集成内部电阻的ADA4077-2表现不错。集 成OVP电路的ADA4177的鲁棒性最好。在某个电源在某个时间段可 能未上电且无法增加外部限流电阻的应用中,推荐使用ADA4177以 避免精度性能下降。

-

电源

+关注

关注

184文章

17567浏览量

249421 -

放大器

+关注

关注

143文章

13545浏览量

213084 -

拓扑结构

+关注

关注

6文章

323浏览量

39159

发布评论请先 登录

相关推荐

关于集成运算放大器电源系统的设计

【转帖】运算放大器电源上电时序导致的风险分析

运算放大器的最大电源电流规格

运算放大器的最大电源电流规格

什么是运算放大器和比较器?

什么是运算放大器和比较器?

运算放大器电源上电时序导致的风险分析

常规运算放大器的自举电路设计

运算放大器的相关资料分享

运算放大器的“最大电源电流” 规格解析

运算放大器相关知识及其应用详述

运算放大器的参考指南

分享关于运算放大器电源上电时序导致的风险避免以及相关研究

分享关于运算放大器电源上电时序导致的风险避免以及相关研究

评论