如今,不仅是高性能FPGA还有其它逻辑器件都正在变得越来越强大了,它们正整合着传统上由其它类型的逻辑器件完成的功能,比如CPU、GPU还有DSP等。它们可谓是瑞士军刀的半导体版本。

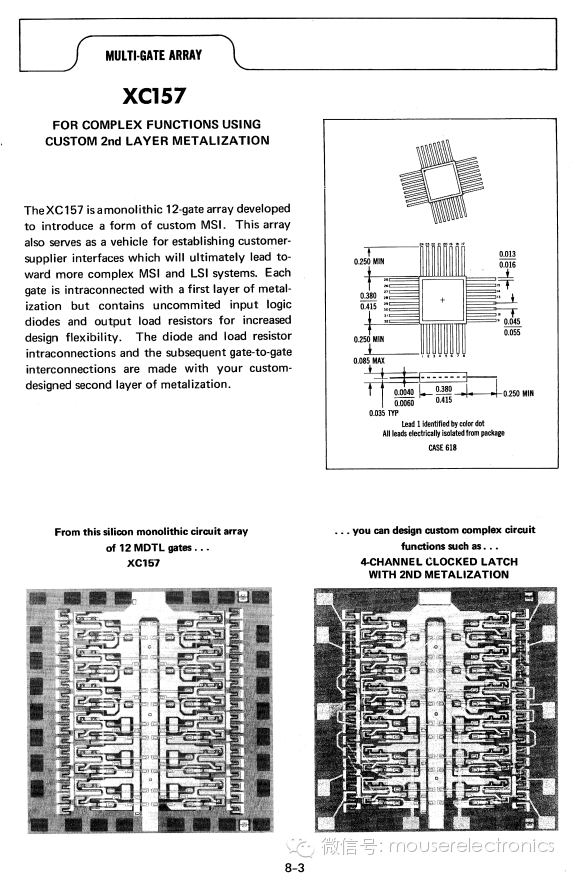

1969年,成千上万人(包括作者本人)聚在乌兹托克音乐节,协和号飞机进行了第一次试飞,尼克松上任,此外还有一件重大的事情在那年发生:带有12个门和30个输入/输出引脚的XC157掩模编程门阵列出现在了1968版古老的摩托罗拉半导体数据手册上(图1)。

用老生常谈的话说就是,接下来的事大家都知道了——由许许多多厂家制造的不同逻辑器件让众多类型的嵌入式系统成为现实。

根据复杂度的相对级别,纷繁复杂的逻辑器件可大致分为三类(表1)。位于表中顶层的是现场可编程器件的霸主——FPGA以及它们的变体——自从1985年David W.Page和LuVerne Peterson发起这个概念后,它们已经有很长的一段历史了。FPGA和它们最相近的兄弟复杂可编程逻辑器件(CPLD)的区别在于它们能够完成复杂功能的能力,它们就像一个“空白的画布”,它们的功能在之后被描绘在画布上,而不是由厂家预先特定地赋予。

图1:如1968版摩托罗拉半导体数据书册上描述的摩托罗拉XC157”多门阵列”感谢:Jason Scott,所有者,textfiles.com

FPGA真可谓是大显神通,因为它们无需外设就可以进行计算、信号处理、高速通信还有其它功能。在一个FPGA上去定义数量庞大的连接和器件逻辑功能从来都不是意见容易的事,也没有必要那样做,FPGA厂商和软件开发商已经开发出来软件工具可以让开发的过程变得轻松。为了加速编程开发过程,也可以使用预先设计的和验证了的知识产权(IP)功能模块。

FPGA这个概念的提出始于19世纪80年代末,它是美国海军水面作战部一个计划的成果,当时业内人士开发出了一个实现了600,000个可编程门的计算机。那不久之后,第一款商业FPGA(XC2064)由赛灵思创始人Ross Freeman和Bernard Vonderschmiitt在1985年推出。该FPGA是个8x8可配置逻辑模块(CLB)格(64个CLB),带有两个3输入查找表(LUT)。

很快到了现在,发展的速度让人吃惊。如今集成ARM Cortex内核或其它处理内核的FPGA能够给DSP、集成ADC每秒执行超过1万亿次的浮点型运算,总吞吐率(所有串行收发通道)达3Tb/s,有超过5千万个逻辑元件,超高速内存(容量很大),还有128位加密。所有的这些甚至还会有更多都包含在这个单一器件上,并且功耗很低,前所未有的低延迟,还有更多让人印象深刻的属性。如今FPGA能够实现这么多不同类型的功能以至于它们现在不仅仅是一个片上系统,同时也是一个更灵活、复杂的系统。例如,以前通讯系统中用到一组ASIC电路来实现前端的接收机功能,如今利用一片FPGA就能搞定。不像ASIC电路那样在制造过程中功能就固定了,FPGA可被再编程,而硬件上没有大体的改变。

FPGA的下一个前沿

下一步FPGA主要应用在可配置计算当中,连同软件一起,它们提供一台计算机的所有功能,利用一个通用处理器作为控制。这并不是一个新概念,它已经在19世纪60年代被人们描述出来了,并于1991年由Algotronix公司的Tom Kean、John Gray博士和David Rees博士在CHS2X4平台上展示出来了。此平台基于该公司的CAL1024 FPGA,有1024个1.5-µm双金属CMOS工艺的可编程器件,并且是第一款能对控制内存提供随机访问的FPGA,也是第一款能够给要构建的设备使能阵列提供输入/输出信号共享的FPGA。这一成就和技术使得赛灵思在1993年收购了Algotronix公司。

在一些特定高性能系统中已经使用FPGA来进行可重新配置计算了,包括加密领域。一个有趣的例子是密码破译机器即成本优化并行代码断路器(COPACOBANA),专门为如数据加密标准(DES)及其它并行计算问题设计。在任何意义上这并不是一个通用用途,因为它的通信受限于速度和带宽,相比基于CPU的电脑,时钟速率也较慢。尽管如此,对于那些适合使用FPGA的应用,成本能够大大降低,并且有很强的性能。通过仅仅使用FPGA还有其它现成的部件,能够使成本仅仅是电子前沿基金的DeepCrack那样基于CPU的加密计算机成本的几分之一。

COPACOBANA(图2)使用了120个FPGA(根据具体设计增减),适配19英尺槽的三个单元。它每秒进行480亿此DES解密,功耗仅为600W,只需要运行Windows或Linux系统的PC机控制就行。在加密硬件和嵌入式系统2006(CHES2006)工作坊的秘钥挑战中,COPACABANA花费了21小时26分钟29秒,以每秒431.852亿值得吞吐率使用了128个处理器中的108个。在搜索了4.7%的秘钥空间后,它找到了秘钥。这种类型的硬件用在常规硬件攻击中通过迭代猜测秘钥或密码来解锁加密的传输。

图2:COPACABANA:基于FPGA的廉价代码破译机。

-

可编程逻辑

+关注

关注

7文章

517浏览量

44284

发布评论请先 登录

相关推荐

可编程逻辑器件

PLD可编程逻辑器件

可编程逻辑器件基础及应用实验指导书

什么是PLD(可编程逻辑器件)

关于可编程逻辑器件的性能分析和应用

关于可编程逻辑器件的性能分析和应用

评论