如果你已经有了一个设计并且想将这个设计移植到另一款目标器件上,这篇文章将帮助你确定这种转换所应遵循的步骤。

这篇文章不会涉及与原设计完全不同的转换方式,从底层组件来看并非完全不同的。

对于这种转换你应该遵循特定的转换指南,比如UltraScale系列转换为Versal系列器件,这篇文章的主题就是这种转换的方法,转换的方式通常是相似的。

设计的 RTL 部分

底层的RTL结构和Verfilog/VHDL代码不需要任何更改。

大部分的实例化原语也不需要任何更改,Vivado工具将会用等效的实例化原语来进行替换来满足目标设计的需要。

可能有一些特定的原语不能进行替换,这可能与最初组件的选择和目标设计的结合有一定关系。对于这种情况,你就需要手动找到最接近的等效功能从而替换之前的原语模块。

对RTL源码进行一次综合操作,不用担心时序约束的正确性,甚至不用去考虑是否是最优的综合。

然后仔细查看综合操作的日志文件,如果你看到某些与无法综合的原语相关的信息,那么这些原语就需要你亲自来替换了。

还要注意那些关键的警告,如果某些原语被重新设计了,但是功能就可能得不到保证。

使用综合操作的日志文件来确定可能需要修改是一种比较快速的方法,而不用遍历所有的RTL源码。

设计的 IP 部分

如果你的设计采用了IP模块,首先你需要检查来确定相同的IP在新的芯片上是否还能够使用。

大部分软核IP在新的目标器件上都应该能够使用,然而硬核IP有可能就不适用了,当然这与选择的器件有关。

你想做的第一件事就是“升级”你的IP组件。

检查IP说明文档或者IP升级日志,这些文件包含更改了哪些参数、管脚输出等详细信息,IP升级日志可以在你的工程目录下找到。

对于采用的所有IP,你要快速检查可以自定义的参数,通常IP的自定义配置可以保留不变,然而在新的设计结构中可能还需要一些额外的参数设置,当然一些参数可能不再适用了,你希望看到的是采用当前的参数设置每个IP的功能都能正常工作。

同样的输入管脚配置也需要修改,如果有必要的话你需要检查管脚输出,更改实例化IP组件的管脚连接。

然后“生成输入文件”——面向新的器件

即使在修改不同组件之前已经执行了“生成输入文件”操作,那些输入文件可能不再有意义,因此需要重新生成。

设计的 IPI/BD 部分

整个设计的IPI/BD部分与IP部分应该非常的相似。

首先要检查一下在BD中使用的IP模块在目标器件上是否可用。

对于设计的BD部分,执行“报告IP状态”操作,升级建议的IP模块。一般来说它会将以对BD中使用的所有IP进行升级。

查看IP升级日志文件,其中包括需要更改哪些参数、输入管脚等详细信息,IP升级日志可以在工程目录下找到。

检查每个IP的参数,可能会增加一些新的参数,一些之前版本的参数可能弃用了,同样的管脚输出也需要修改。

如果管脚输出被更改了,你应该能够借助自动化连接操作来找回丢失的连接。

一旦BD部分为新的设计准备好了,那么就可以执行“验证BD”操作了,验证成功后执行“生成输入文件”操作即可。

检查BD级的管脚输出是否仍然保持不变,否则就需要重新实例化BD模块并且更新BD模块的管脚连接。

I/O 管脚规划和布局

如果有需要还要根据新的目标器件的管脚输出重新执行I/O布局操作。

实现步骤

一旦IP(包括工程目录下的和BD目录下的)都进行了更新,那么整个设计还需要重新执行编译操作,包括综合(synthesis)和实现(implementation)等操作。

在验证过程中还需要对实现策略、执行顺序、管脚规划布局以及LOC约束进行仔细的检查。

最后感谢来自CortexRF公司的格伦·英格利希(Glen English)对本篇文章的建议,确认了设计转换器件过程中要注意的事项和操作步骤,从而保证整个设计的正常工作。

-

转换器

+关注

关注

27文章

8701浏览量

147143 -

IP

+关注

关注

5文章

1705浏览量

149525 -

器件

+关注

关注

4文章

310浏览量

27829

发布评论请先 登录

相关推荐

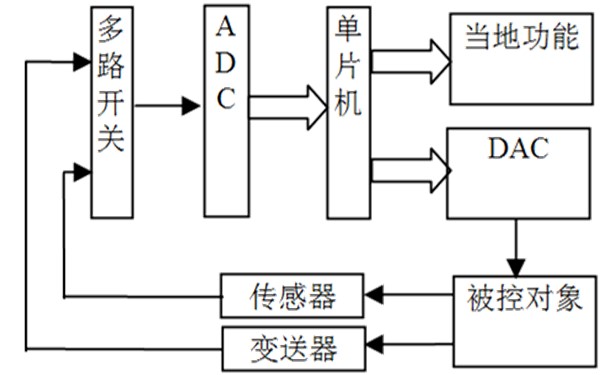

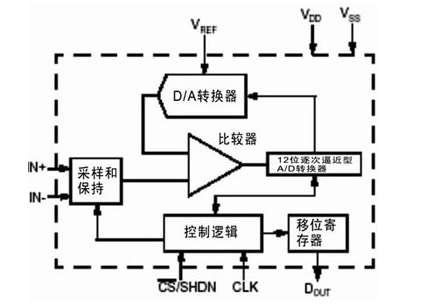

A/D转换器概述及分类

数模转换器是什么

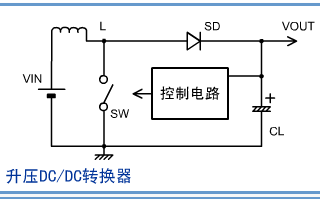

DC/DC转换器,DC/DC转换器是什么意思

模数转换器和数模转换器概述

如何选用DC/DC转换器IC外围器件?

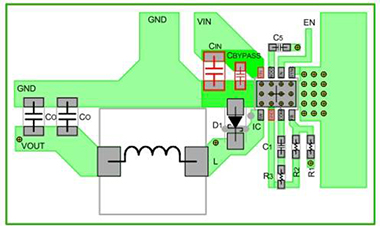

DC/DC转换器的基板布局-DC/DC转换器的PCB板布局概述

A/D转换器所需的PCB布线策略

设计转换器和器件移植概述

设计转换器和器件移植概述

![RA6T2的16位模数<b class='flag-5'>转换器</b>操作 [1] 简介,A/D<b class='flag-5'>转换器</b><b class='flag-5'>概述</b>](https://file1.elecfans.com/web2/M00/BB/1B/wKgZomWXtb6ACk_NAAARMuEl9ZA261.png)

评论