赛灵思可编程器件含有数百万个逻辑单元 (LC),集成了当前越来越多的复杂电子系统。《UltraFAST 高层次生产力设计方法指南》为广大开发者提供了在短设计周期内开发此类复杂系统的一套最佳做法。

这种方法以下列概念为重点:

对宝贵的差异化逻辑使用并行开发流程,实现您的产品在市场上的差异化,且 shell 可用于将 IP 与生态系统的其它部分集成。

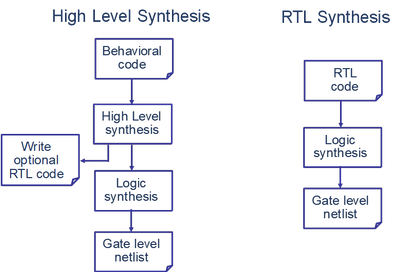

广泛使用基于 C 语言的 IP 开发流程开发差异化逻辑,让仿真速度相对于 RTL 仿真成倍增长,并且能提供时序准确和得到优化的 RTL。

使用现有的预验证、块和组件级 IP 来快速构建 shell,将差异逻辑封装在系统中。

使用脚本,针对从准确设计验证直至编程 FPGA 的流程实现高度自动化。

本指南中的建议是来自多位专家级用户多年的经验总结。与传统的 RTL 设计方法相比,该指南提供了下列改进:

设计开发时间加快 4 倍;

衍生设计开发时间加快 10 倍;

结果质量 (QoR) 提高 0.7 倍到 1.2 倍。

虽然本指南以大型复杂设计为重点,但所讨论的实践也适用于且已被成功地应用到各种类型的设计中,包括:

处理器加速

无线

存储

我是分割线

目 录

-

控制系统

+关注

关注

41文章

6508浏览量

110376 -

赛灵思

+关注

关注

32文章

1794浏览量

131123 -

可编程

+关注

关注

2文章

831浏览量

39747

发布评论请先 登录

相关推荐

Vivado 高层次综合

高层次综合工作的基本流程

SOC设计中高层次功耗估算和优化技术

使用Vivado高层次综合 (HLS)进行FPGA设计的简介

Vivado Design Suite HLx 版本 2016.4 现已发布

了解最新的UltraFast设计方法窍门与技巧

Xilinx发布唯一SoC增强型Vivado设计套件,可大大提高生产力

揭示高层次综合技术工作的基本概念

高层次综合技术原理浅析

【开源硬件】从PyTorch到RTL - 基于MLIR的高层次综合技术

使用Vivado高层次综合(HLS)进行FPGA设计的简介

《UltraFAST 高层次生产力设计方法指南》简介

《UltraFAST 高层次生产力设计方法指南》简介

评论