这里的 UIO 即 Userspace I/O,本文中 UIO 泛指 UIO 设备和 UIO 驱动。它在 Linux kernel 的世界里比较小众,主要是一些定制设备和相应的驱动。UIO内核驱动指负责将中断和设备内存暴露给用户空间,再由UIO用户态驱动(Application)来实现具体的业务,随心所欲的玩。学术点叫做高度定制化,柔性设计。

那怎么和 FPGA 扯上了关系呢?是的,FPGA在硬件世界里也是随心所欲的玩,这一硬一软还真是登对,在一起啊在一起。

本实验工程将介绍如何利在赛灵思异构多处理器产品系列 Zynq UtralScale+ MPSoC ZCU102 嵌入式评估板上实现多个 UIO,同时借助赛灵思的工具完成硬件工程和 linux BSP 的开发,最后通过测试应用程序完成测试。

ZCU102上的 MPSoC 集成固化了四核 ARM Cortex-A53,双核Cortex-R5 以及 Mali-400 MP2 GPU,这部分官方称为PS(Processing System)。另外一部分就是FPGA,即 PL(Programmable Logic)。PS端实现控制,PL用来实现应用加速,两者通过AXI连接。跑这个小实验,呵呵,大材小用。只是本人手头正好有这个板子不得不装。筒子们可以去买了个Zybo 或者ZedBoard 开发板, 在板子试试身手。

实 验 报 告

实验人员:本人

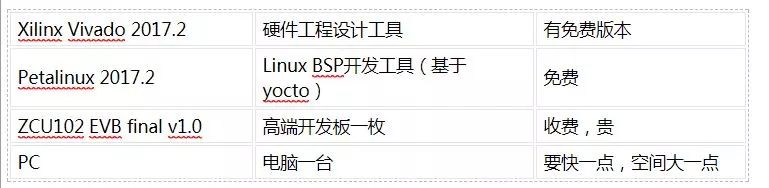

实验材料:

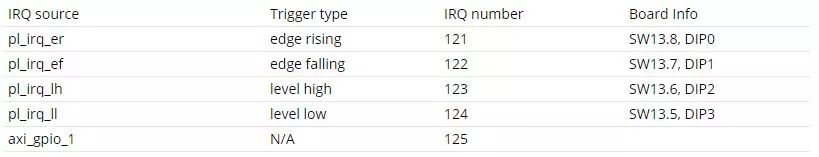

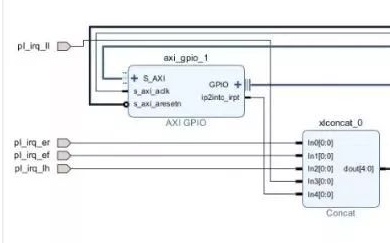

硬件设计

建立Vivado工程,适配 ZCU102 EVB。通过 IP Integrator 加入PS,在 PL 侧加入5个UIO输入,其中1个是GPIO模块(包含中断输出和设备内存),另外4个是PIN连接到ZCU102 EVB上的DIP开关,作为中断输入通过一个concat IP连接到PS的ps_pl_irq管脚。板级细节请参考[1] UG1182,芯片资料参考[2] UG1085

添加PIN约束文件,

set_property PACKAGE_PIN AN13 [get_ports pl_irq_ll]

set_property IOSTANDARD LVCMOS33 [get_ports pl_irq_ll]

set_property PACKAGE_PIN AM14 [get_ports pl_irq_lh]

set_property IOSTANDARD LVCMOS33 [get_ports pl_irq_lh]

set_property PACKAGE_PIN AP14 [get_ports pl_irq_ef]

set_property IOSTANDARD LVCMOS33 [get_ports pl_irq_ef]

set_property PACKAGE_PIN AN14 [get_ports pl_irq_er]

set_property IOSTANDARD LVCMOS33 [get_ports pl_irq_er]

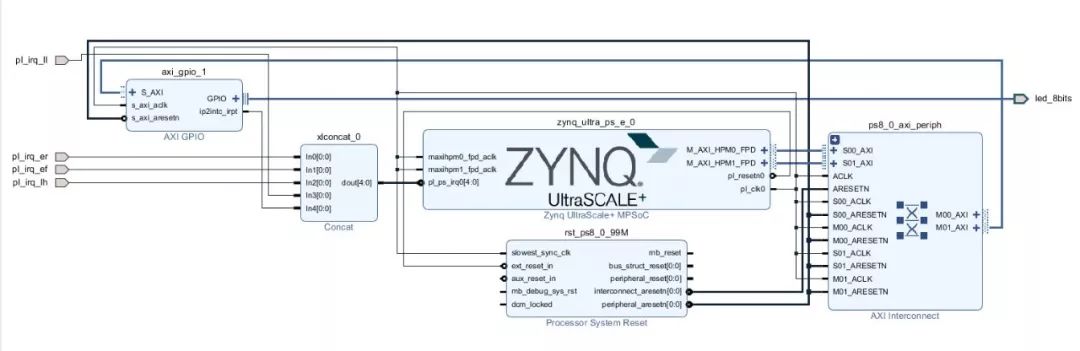

Vivado的图形化的模块设计,丰富的IP库,加上可以上天的智能连接。有点数字电路设计的基础,很快就能完成这个小设计。整个设计如下图。

软件设计

这里用到 Xilinx 针对 Linux BSP 开发的 Petalinux。它基于Yocto,加入Xilinx的Layers实现硬件工程的导入,将复杂的Yocto的设计流程打包简化,支持一定的用户自定义功能,如QEMU仿真运行,增加 out-of-tree 的驱动,Device tree 修改,应用程序编译打包,等等。

这里简单展示一下具体的命令过程。

$petalinux-create -t project --template zynqMP -n zcu102-pl2ps_irq

$cd ./ zcu102-pl2ps_irq

$petalinux-config --get-hw-description

$petalinux-config -c kernel

Enable UIO_PDRV_GENIRQ driver

CONFIG_UIO=y

# CONFIG_UIO_CIF is not set

CONFIG_UIO_PDRV_GENIRQ=y

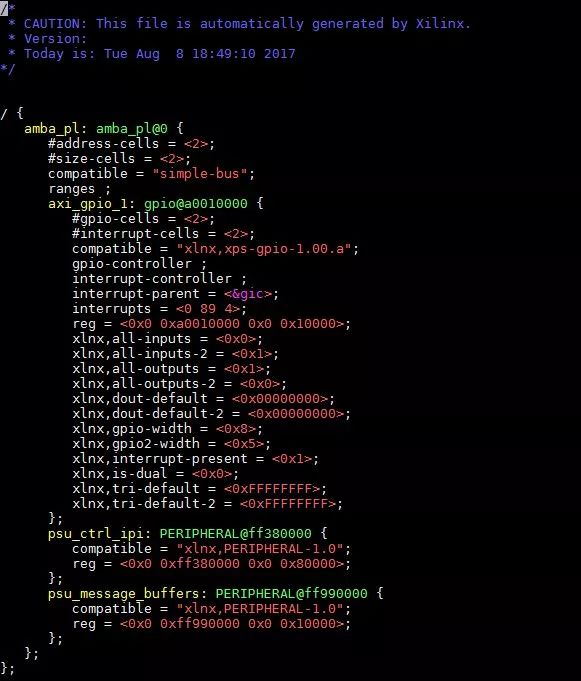

$petalinux-build -c device-tree

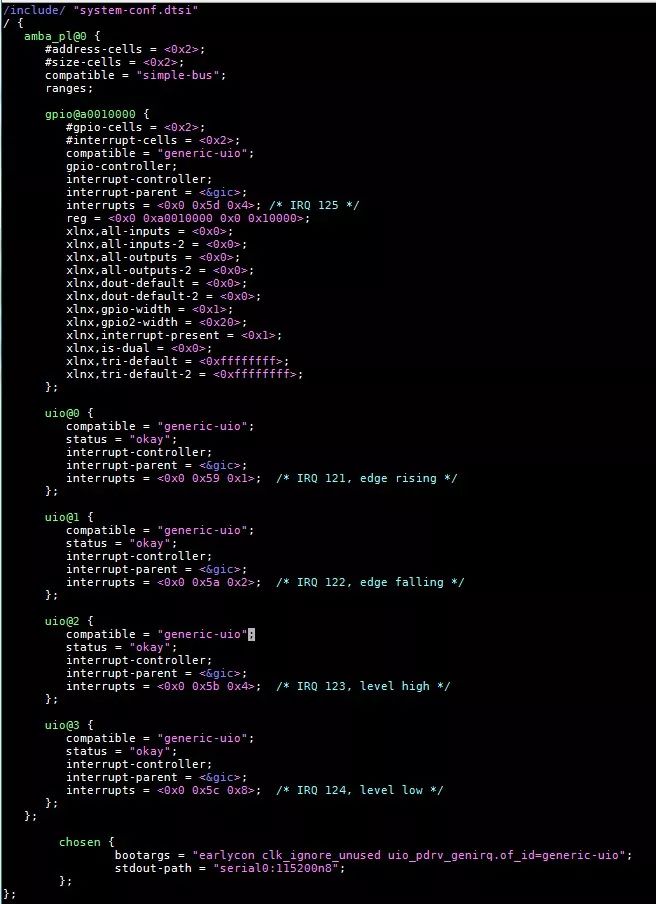

PL侧的dtsi文件生成与./components/plnx_workspace/device-tree-generation/pl.dtsi

这里只有GPIO UIO。 PIN UIO因为不是IP,所以相关信息无法由工具自动生成。所以要做如下修改:

1. 修改GPIO UIO设备端点

1) 将中断号改为93

2) 将compatible改成“generic-uio” //我们后面要用 Linux 自带的 UIO_PDRV_GENIRQ 驱动

2. 增加 DIP UIO 端点

1) 将compatible改成“generic-uio”

2) 依次设置中断值89到93

3) 按照每个 DIP PIN 的 interrupt trigger type 设置属性值

*DTS里的中断号与硬件中断号有32的 offset。

Petalinux 提供了自定义DTS文件./project-spec/meta-user/recipes-bsp/device-tree/files/system-user.dtsi,将以上修改定义到system-user.dtsi.

有两个方法来适配UIO端点和 UIO_PDRV_GENIRQ 驱动

1. bootargs use “uio_pdrv_genirq.of_id=generic-uio”,可以通过DTS定义。

2. insmod uio_pdrv_genirq.ko of_id=generic-uio when install the driver

修改完后,编译出Image.

$petalinu-build

$cd ./images/linux

$petalinux-package --boot --fsbl zynqmp_fsbl.elf --fpga --atf --pmufw --u-boot --force

将生成的BOOT.bin(bootloader)和image.ub(FIT uImage)拷贝到SD卡用于启动。\

测试

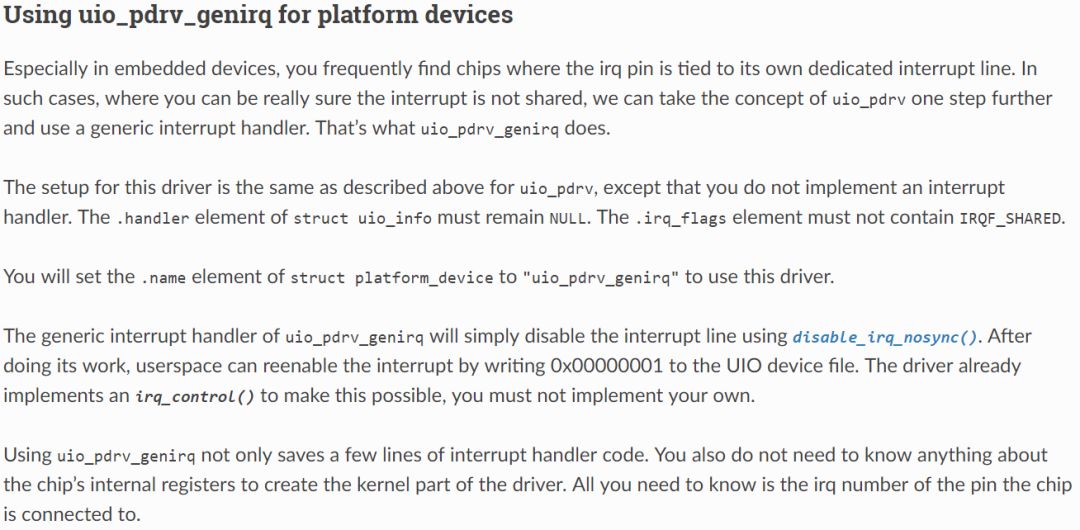

这里引用下关于uio_pdrv_genirq驱动的介绍

https://01.org/linuxgraphics/gfx-docs/drm/driver-api/uio-howto.html

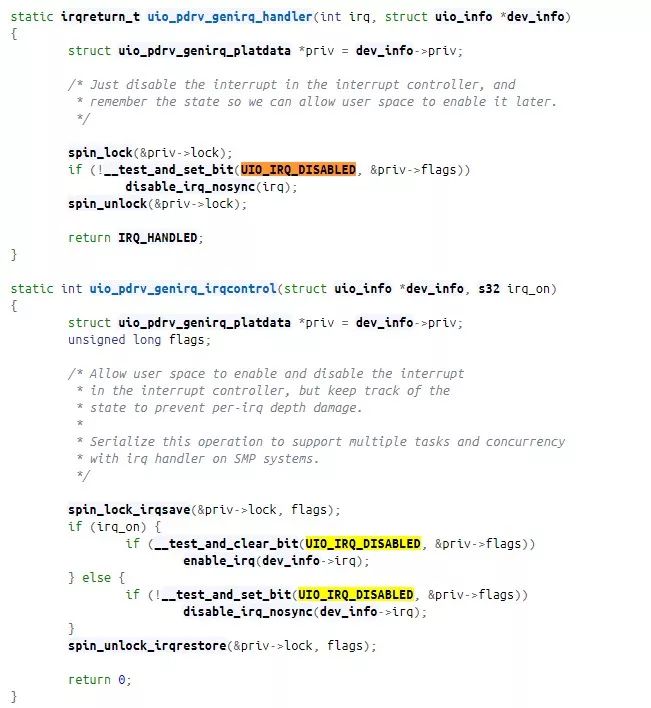

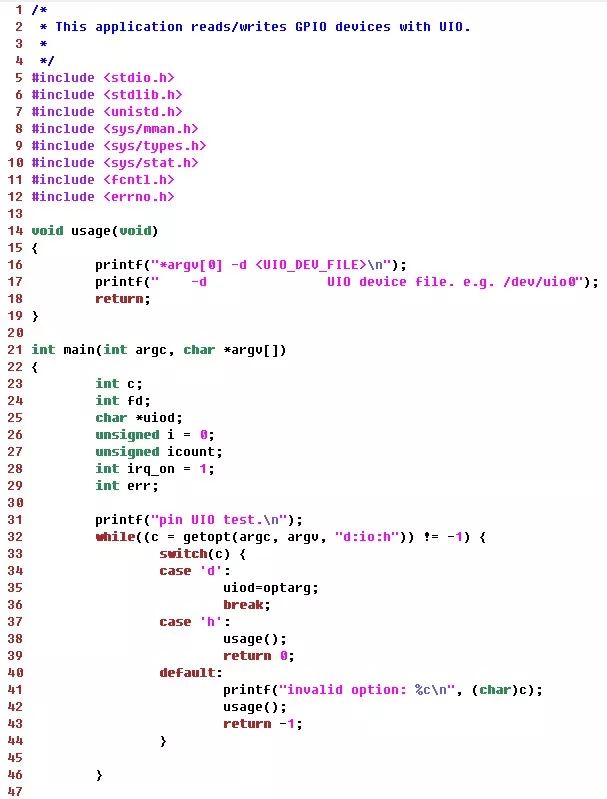

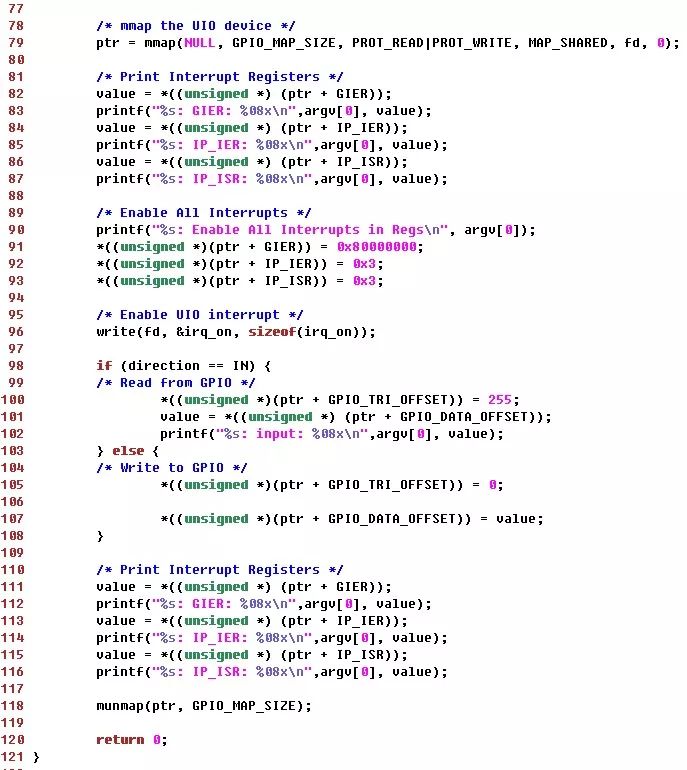

结合驱动代码./drviver/uio/uio_pdrv_genirq.c)可知,每个UIO设备会有对应的/dev/uioX的设备节点。用户态驱动程序的读操作会阻塞直到UIO硬件中断发生。UIO的中断处理程序uio_pdrv_denirq_handler()会关闭该硬件中断。用户态驱动程序需要通过write函数来触发uio_pdrv_genirq_irqcontrol()以完成中断的使能和关闭。代码如下,

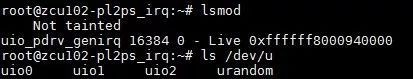

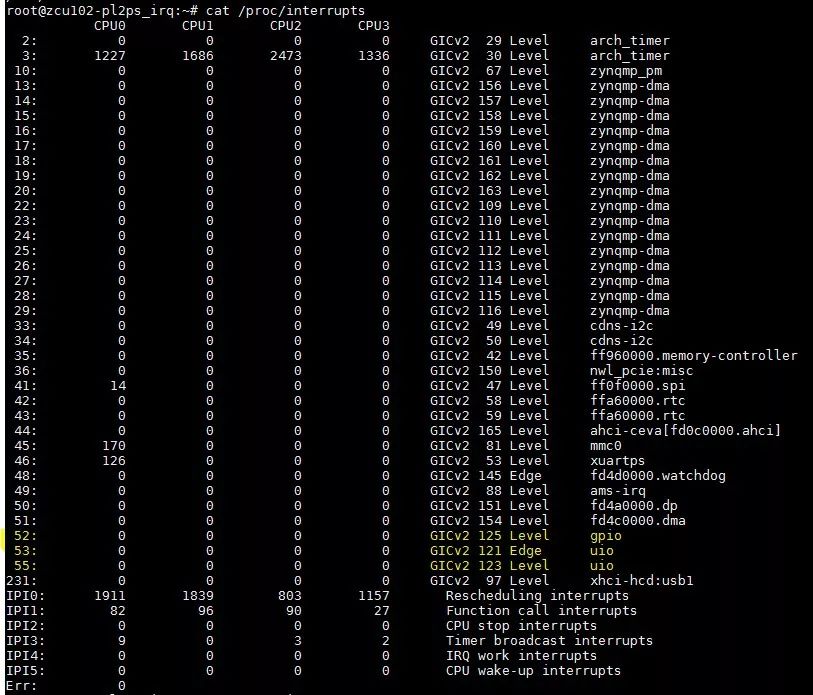

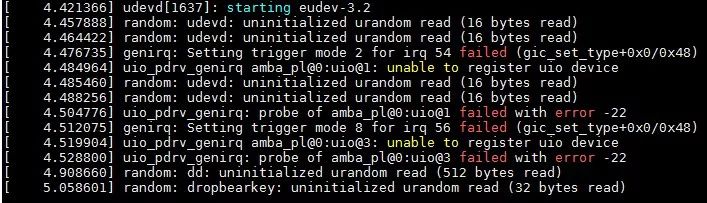

启动内核及加载uio_pdrv_genirq驱动

检查/proc/interrupts

细心的你一定发现了一个坑,少了2个UIO中断(IRQ122和IRQ124),原来是硬件不支持Edge falling和Level Low的触发模式。kernel log如下。

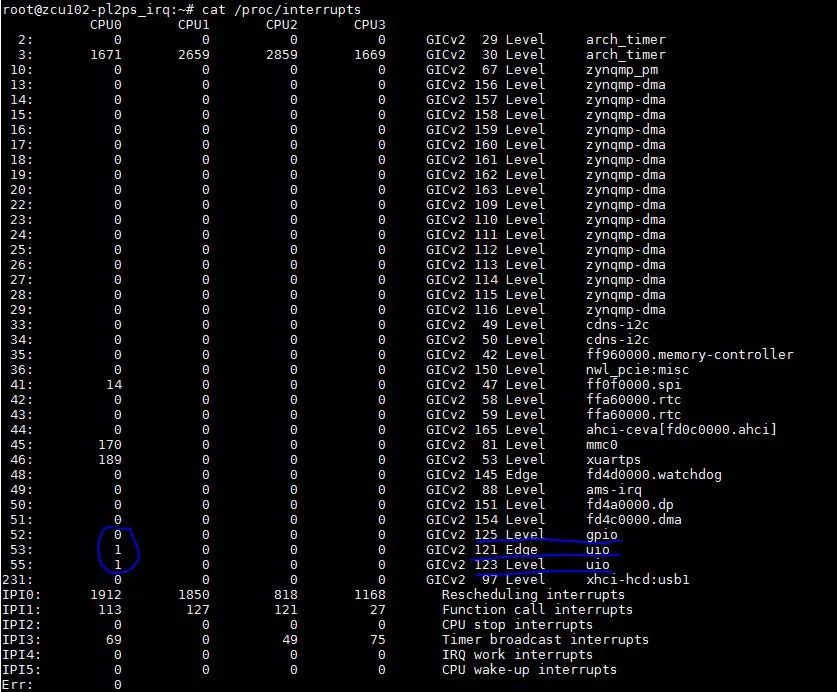

测试DIP UIO方法一

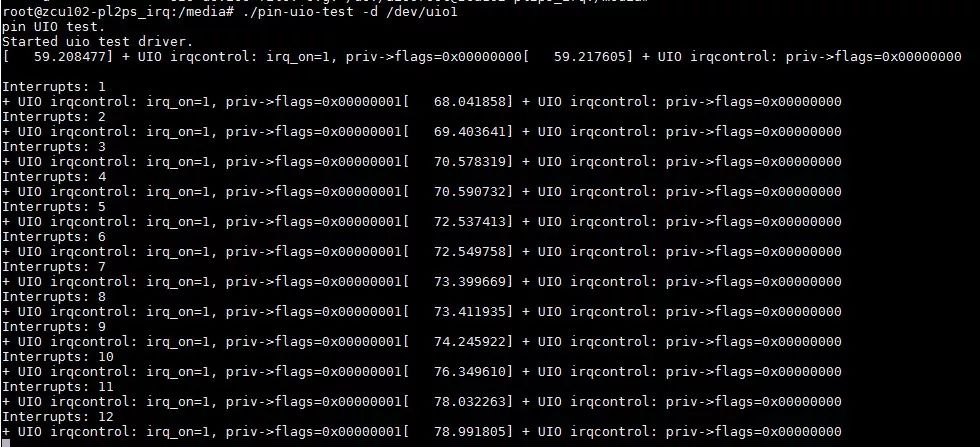

通过拨动2个DIP,观察到

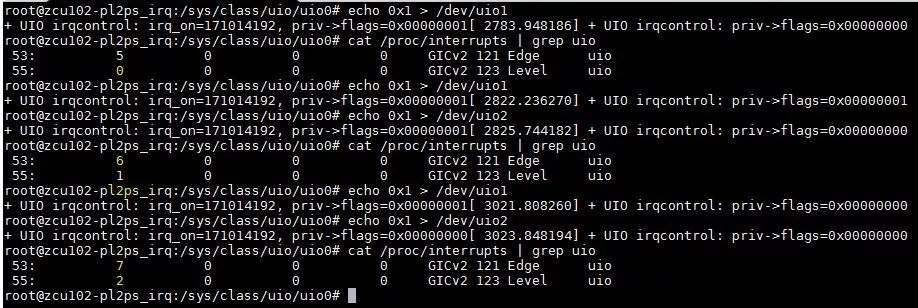

2个DIP中断发生了,可是不论怎么再拨动DIP开关,始终是1。前文铺垫过,这个中断在驱动的中断处理程序里会被关掉,需要通过应用程序调用write()来打开。这里有个easy way,使用万能的echo命令“echo 0x1 > /dev/uioX”,再配合DIP可以触发多次中断。

测试DIP UIO方法二

前面的方法比较low,这里有稍微高级的享受。写个简单的用户态驱动程序,上代码。

借助petalinux提供的交叉编译工具编译出bin文件,拷贝到启动SD卡。

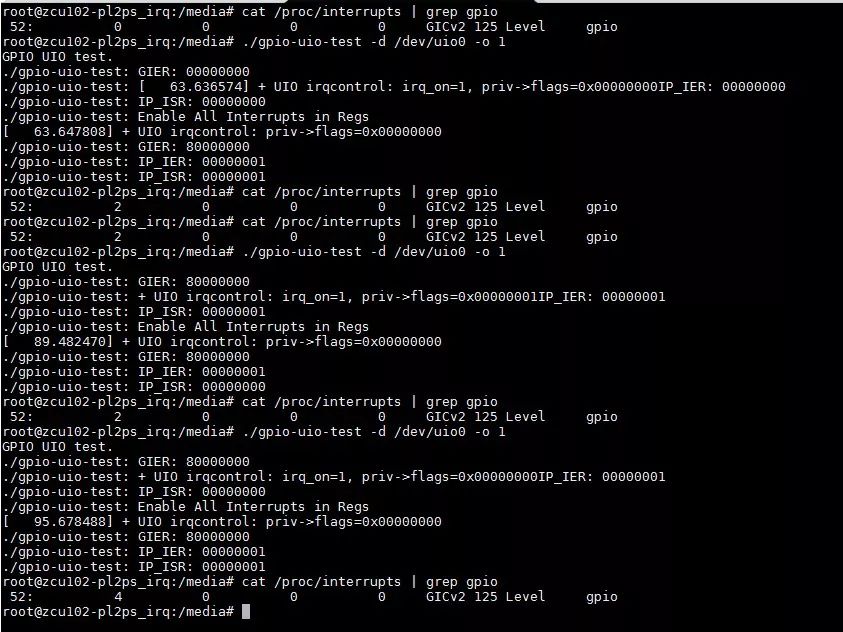

运行测试程序并配合DIP开关测试。(为了更好的体现测试运行情况,在UIO内核驱动里增加了irqcontrol的调用打印)

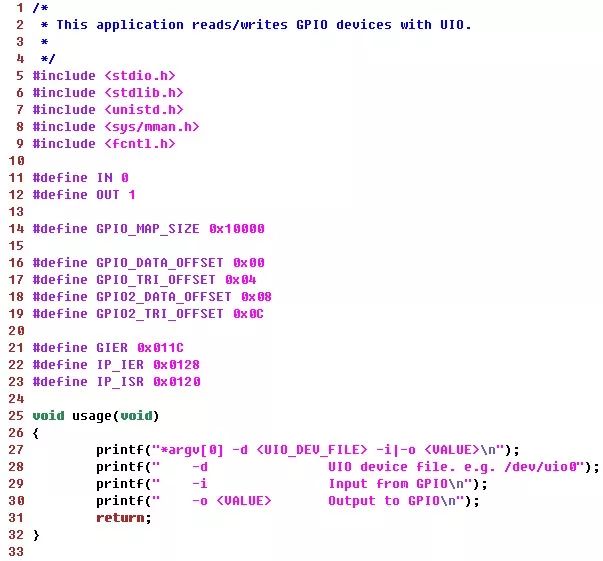

测试GPIO UIO

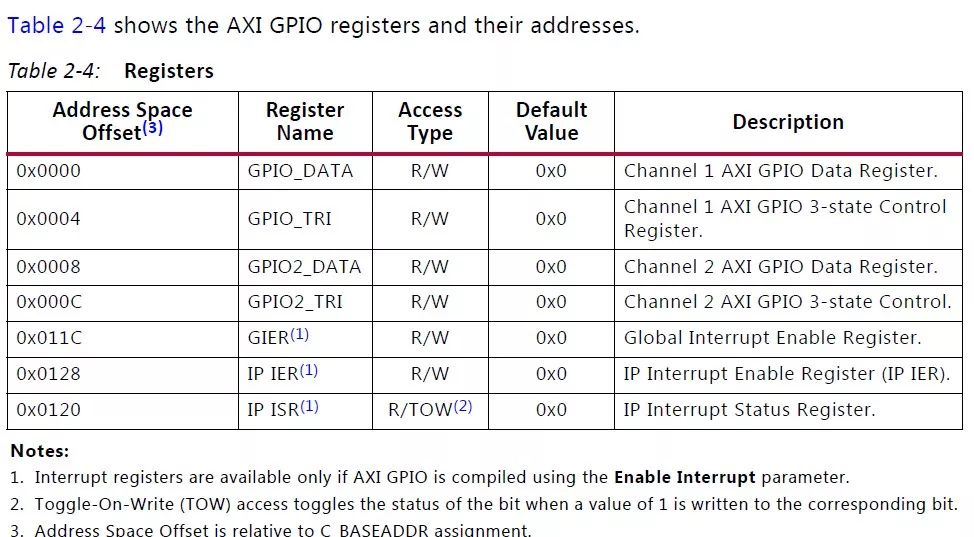

UIO驱动会将设备内存(寄存器)空间枚举出来,由用户态驱动程序通过mmap导出进行读写控制。参见AXI_GPIO IP的文档pg144-axi-gpio.pdf,其寄存器如下。

测试应用程序会通过设置GIER和IP_IER来使能中断。上代码。

测试过程

或许你觉得这么贴图代码不厚道而不能施展复制黏贴大法,可不知我拙与WORD,没try出好排版。莫急莫急,这里有GIT,

实 验 结 论

UIO这种可高度自定义的设备结合Xilinx的MPSoC可以实现非常灵活的应用。Xilinx提供的完备的工具集,给用户带来了高效的开发体验。本例虽然简单,但Xilinx所推崇的All Programmable的概念和实际的FPGA加速应用的的确确是建立在这些软硬件协同技术之上。忘周知!

-

开发板

+关注

关注

25文章

5040浏览量

97409 -

编译

+关注

关注

0文章

657浏览量

32863 -

异构多处理器

+关注

关注

0文章

4浏览量

9664

发布评论请先 登录

相关推荐

为嵌入式系统选择合适的多处理器(一)

多核处理器SoC设计怎么才能满足嵌入式系统应用?

异构多处理器系统Cache一致性解决方案

赛灵思强化嵌入式视觉应用与工业物联网产品系列

面向异构多处理器设备的自适应命令解释系统

嵌入式视觉应用于机器学习的设计方案

性能优良的赛思灵FPGA嵌入式处理器平台

GPGPU流式多处理器架构剖析(上)

在赛灵思异构多处理器产品系列嵌入式评估板上实现多个 UIO

在赛灵思异构多处理器产品系列嵌入式评估板上实现多个 UIO

评论