目前,在高层次综合(HLS, High Level Synthesis)领域,Vivado HLS可谓独树一帜。它有效地拉近了软件工程师与FPGA之间的距离,加速了算法开发的进程,缩短了产品上市时间。对于工程师,尤其是软件工程师而言是一个福音。在实际工程中,如何利用好这一工具仍值得考究。本文将介绍使用Vivado HLS时的几个误区。

误读1:只要是 C/C++ 描述的算法都是可综合(可转换成 RTL)的。

HLS的可综合功能是有限的,并不是所有的C或者C++语句都可转换成相应的RTL代码。下面这些情形是不可综合的。

○ 动态内存分配

○涉及操作系统层面的操作

○递归函数

○数组规模可变

误读2:既然Vivado HLS支持C、C++和System C,那么用三者任意一种都行。

尽管 Vivado HLS支持C、C++和System C,但支持力度是不一样的。在v2017.4版本ug871 第56页有如下描述。可见,当设计中如果使用到任意精度的数据类型时,采用C++ 和System C 是可以使用Vivado HLS的调试环境的,但是C 描述的算法却是不可以的。而实际上很多真实的硬件模型都要使用任意进度的数据类型,所以要想使用Vivado HLS 的调试功能, 建议最好采用 C++和System C。

误读3:只要有源代码即可,没有Test bench也行。

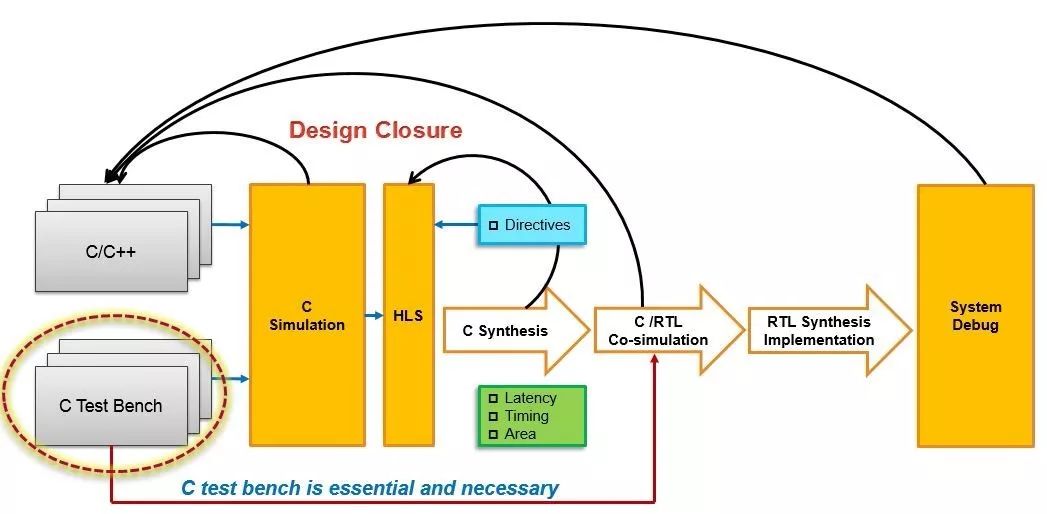

在HLS设计开发中,C Test bench起着举足轻重的作用。C层面算法功能的验证需要用到它;当生成RTL代码时,C和RTL的协同仿真也要用到它。如下图所示。实际上,协同仿真时,RTL代码的输入激励就是由C Test bench生成的。由此可见,C Test bench是整个设计不可或缺的一部分。

-

C++

+关注

关注

22文章

2104浏览量

73480 -

源代码

+关注

关注

96文章

2944浏览量

66657

发布评论请先 登录

相关推荐

探索Vivado HLS设计流,Vivado HLS高层次综合设计

vivado HLS 综合错误

请问如何只下载Vivado HLS 2015.2

来自vivado hls的RTL可以由Design Compiler进行综合吗?

Vivado HLS许可证问题如何解决

Vivado HLS设计流的相关资料分享

Hackaday读者有话说:Vivado HLS使用经验分享

用Vivado-HLS实现低latency 除法器

如何创建Vivado HLS项目

如何使用Tcl命令语言让Vivado HLS运作

将VIVADO HLS设计移植到CATAPULT HLS平台

关于Vivado HLS错误理解

关于Vivado HLS错误理解

评论