背景:

快速傅里叶变换(FFT)在雷达、通信和电子对抗等领域有广泛应用。近年来随着现场可编程门阵列(FPGA)的飞速发展,与DSP技术相比,由于其并行信号处理结构,使得FPGA能够很好地适用于高速信号处理系统,但是,由于Altera等公司研制的FFT IP核,价钱昂贵,不适合大规模应用,在特定领域中,设计适合于自己领域需要的FFT处理器是较为实际的选择,下面将关注一些关于流水级FFT处理器的一些最新发展。

SDF FFT Core → FPGA DSP slice:

近期,在IEEE VLSI系统专栏学报处有一篇12页的题为“Efficient FPGA Mapping of Pipeline SDF FFT Cores”的新论文即将被发表(在IEEE Xplore可见)。而在这篇论文中作者就如何将一个SDF(single-path delay feedback单路延迟反馈)FFT核映射到Xilinx的全可编程芯片内部的DSP48 slices的可编程逻辑及其他可用的存储资源上进行了深入周密的细节性讨论。尽管这篇论文主要是针对Virtex-4和Virtex-6系列FPGA进行讨论的,但是作者也明确指出,由于Xilinx 7系列和UltraScale/UltraScale+ 系列FPGA与Virtex-6使用相同的slice 架构,所以这种映射其实很容易被推广的。

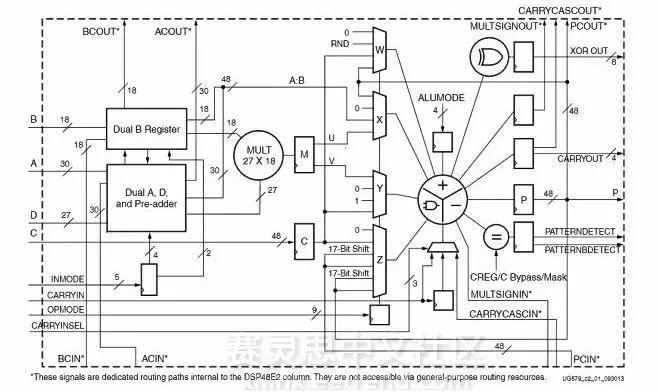

在论文中,作者详细阐述了Xilinx的产品,主要是从Virtex-4 FPGA开始到Xilinx后来的所有全可编程芯片等多代产品内部的DSP48 slices的一个发展过程:首先,Virtex-4 FPGA系列包含一18X18bit乘法器和48bit累加器的XtremeDSP(DSP48);之后的Virtex-6系列FPGA加入了25x18bit乘法器和48bit累加器的DSP48 slices ;较新的7系列FPGA和Zynq-7000系列SoC则内嵌了25x18bit乘法器和48bit累加器的DSP48 slices;而最强的UltraScale/UltraScale+系列FPGA则包括了27x18bit乘法器和48bit加法器的DSP48E2。除此之外,在Xilinx每一代FPGA的DSP48 slices的发展中都有很多额外的改进,比如时钟率具有较稳定的提高,也正是这么多代产品的不断迭代,才使得现在的DSP48E2 功能更加强大。下图是论文中作者提到的关于DSP48E2 功能实现的细节。

图1 DSP48E2 功能细节

同时,在这片IEEE的论文中还讨论了如何将此FFT核蝶形转换到较少的LUT单元中,而如何有效转换关系到是否可以实现DSP48 preadders的蝶形地址,在实现过程中,通过将有效的数据映射和转换因子存储到BRAM 及分布式存储资源中,有效地完成 radix-2k算法转换因子的共享,此外采用重新定时和流水的方式来缩短实现时间。

虽然这篇博客展示的任何技术都是来自于论文中,读者也可以从IEEE论文网站得到,但是还是会给出论文中的一些结论(以便可以提起您去检索并阅读全文的兴趣):“报告的实现结果表明,相比于之前的有关实现而言,通过利用Virtex-4和Virtex-6内部的DSP48实现一个FFT核,可以使其性能分别提高350%到400%,同时,还可以获得一个更高的混合时钟频率,并且整个实现过程只需要更少的存储资源。这也正好如以前发表过的最好的报告结果一样,都是使用完全一样的架构,使用同Virtex-4完全一样的算法,也体现出这种转换的优势十分明显,所以,为提高性能,可以尝试将架构映射到FPGA硬件结构中来实现。

总结:

在目前的市场中,尤其是一些互联网公司,都开始利用FPGA做硬件加速的实现,不仅是因为FPGA的可用性,更主要的是各大公司都看中了硬件实现软件算法时对整个算法质量的极大提升,这类市场也恰好是我们Xilinx未来竞争的关键点所在。

-

算法

+关注

关注

23文章

4619浏览量

93041 -

硬件

+关注

关注

11文章

3345浏览量

66288 -

软件

+关注

关注

69文章

4968浏览量

87682

发布评论请先 登录

相关推荐

采用FPGA实现DisplayPort详细教程【赛灵思内部资料】

FPGA设计之浮点DSP算法实现【赛灵思工程师作品】

赛灵思公司亚太区销售与市场副总裁给XILINX客户的信

【AD新闻】赛灵思新CEO访华绘蓝图,7nm ACAP平台要让CPU/GPU难企及

【PYNQ-Z2申请】基于赛灵思PYNQ-Z2平台的图像实时力学测量

基于赛灵思FPGA的卷积神经网络实现设计

为什么说赛灵思已经远远领先于Altera?

从赛灵思FPGA设计流程看懂FPGA设计

不仅服务硬件工程师_2018年赛灵思如何布局AI

赛灵思推出高级设计工具,能大幅简化无线电算法的设计生产力

赛灵思推出首个基于机器学习优化算法 FPGA EDA 工具套件

赛灵思Vivado ML版优化应用设计

赛灵思未来竞争的关键点:硬件实现软件算法时对整个算法质量的极大提升

赛灵思未来竞争的关键点:硬件实现软件算法时对整个算法质量的极大提升

评论