2011 年,我开始加入 Xilinx 公司,当时 Xilinx 正处于启动从 ISE 到 Vivado 设计套件的转型期。在 Xilinx 的最近几年对我来说是一个非常棒的学习阶段,除了学习到专业的技术知识,同时也看到了Xilinx不断推陈出新,引领设计潮流。

Xilinx 努力做出的变化有:

1. 让其FPGA或者SoC产品都能够适用于ISE和Vivado工具。

2. 从输入和输出格式来讲,让Vivado工具尽可能的兼容行业标准(尤其是不同于ISE)。

3. 增加了功能更强大的算法和引擎支持,这也会带来不同的结果。

在这段时间里虽然我看到很多熟悉ISE的老用户正在从ISE转向Vivado,但是对于那些熟悉行业标准和工具的新用户而言,好像不那么顺利。所以,在这里我分享一点儿我对Xilinx目前工具/解决方案的看法和技巧。同时也会有一些技术文章介绍Xilinx工具的使用方法或者解释某个具体操作的原理和功能。

为什么CPR操作得出的效果却是相反的?

在进行时序分析时片上工艺差别通常会导致严重的“时钟悲观效应”。这种问题可以通过CPR(Clock Pessimism Reduction)操作来恢复.然而经常有用户咨询我们说在他们的设计中CPR操作并没有降低“时钟悲观效应”,效果却是相反的,在时序上并没有增加反而离时序要求差的更多了。

在setup分析时,CPR通常会被添加到目标(目的)时钟路径,因此增加了要求时间。然而因为在用户的设计中CPR已经从目标时钟路径中移除,要求时间变得更早,而不是延后。结果就是用户认为他们损失了时间,而不是获得补偿时间。其实实际情况是用户没有任何损失。

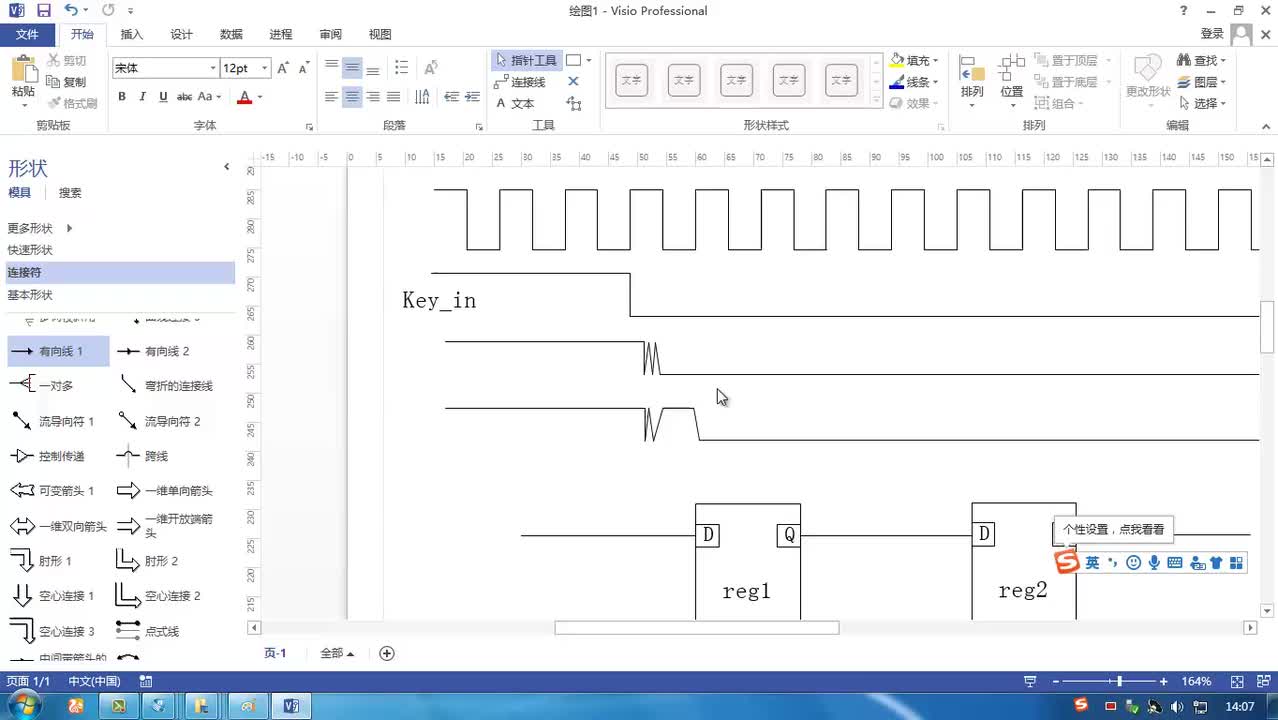

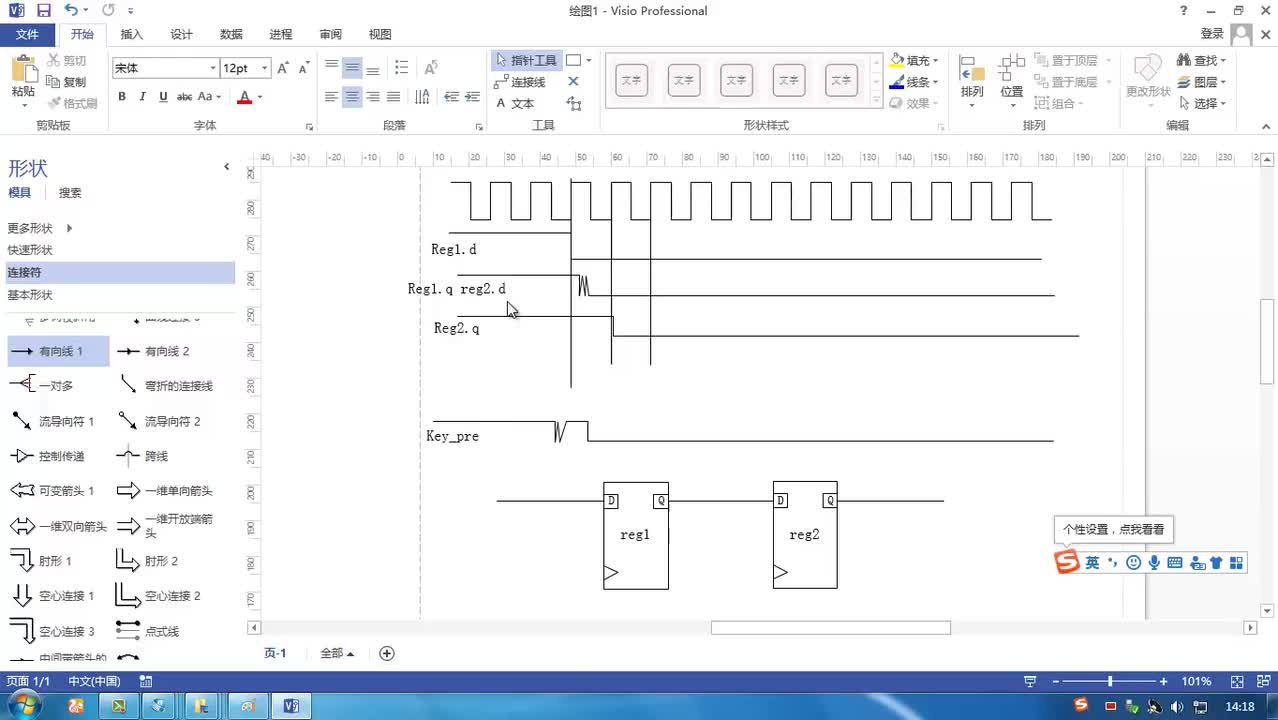

进行OCV分析时,源路径和目标路径被认为具有不同的延迟时间。然而对于两者“共用”的路径,其延迟时间是保持不变的。CPR补偿了延迟差异,因此直到公用节点延迟数值变得一样了。

为了能够更好的理解发生了什么,请查看附件的时序分析报告。

(感谢Xilinx Tokyo的Matsuyama-san分享了他的一个示例设计的时序分析报告)

为了简单易懂,这个报告作了一些修改。在MMCME3_ADV_X1Y2之前源时钟和目标时钟都共享一个公用路径,然后源时钟走向BUFGCE_X1Y48节点,而目标时钟走向 BUFGCE_X1Y50节点。

让我们明确一下公用节点前的延迟(Vivado认为MMCM的输出作为公共节点,尽管两种时钟路径的输出管脚是不一样的)。

让我们看一下时序报告中源时钟路径:

时钟起点是:0(时序报告的21行),到达MMCM的输出端是-3.218(时序报告的31行)。因此公用节点前的延迟是-3.218。

对于目标时钟路径:

时钟起点是:3.33(时序报告的41行),到达MMCM的输出端是0.141(时序报告的50行),因此公用节点的延迟(目标时钟路径)是0.141-3.33=-3.189。目标路径的延迟(-3.189)看起来要比源时钟路径延迟(-3.218)要大一些(注意负号,不要仅看到延迟的数值)。

因此目标路径具有更高的延迟,需要进行补偿。因此在目标时钟中降低“时钟悲观效应”,这样才能减少要求时间。

现在,源时钟和目标时钟在公用节点之前都具有了相同的延迟,也就是说用户在公用节点(如示例中的MMCM节点)前没有任何损失也没有额外获得什么。

这种相反效应的现象在MMCM节点中是存在的,相对UltraScale系列器件,这种情况在7系列器件中更是普遍存在的。

赛灵思公司工具与方法学应用专家,1993年毕业于印度理工学院电子工程专业,一直从事 VLSI 和 EDA 相关领域的工作。2011年加入赛灵思公司,专攻库特性描述与建模,HDL,仿真与综合,静态时序分析以及跨时钟域(CDC)与同步相关内容。

-

FPGA

+关注

关注

1629文章

21751浏览量

604114 -

时序分析

+关注

关注

2文章

127浏览量

22572

发布评论请先 登录

相关推荐

用于Xilinx和Altera_FPGA的电源管理解决方案

AnDAPT为Xilinx Zynq平台FPGA和SoC设备推出完整电源解决方案

Xilinx Virtex Ultrascale FPGA MGT电源解决方案

Xilinx 400GE解决方案的展示

MIPI和Xilinx MIPI解决方案的介绍

设计解决方案41-基于Xilinx FPGA系统的双输出DC/DC转换器解决方案

Xilinx目前工具/解决方案的看法和技巧

Xilinx目前工具/解决方案的看法和技巧

评论