赛灵思 5 月 27 日宣布, 在其 UltraScale+ 全可编程器件发展蓝图上新增存储器带宽快车道(Xilinx 扩大 16nm UltraScale+ 产品路线图为数据中心新增加速强化技术)。这种新型高速路由将 3D HBM(高带宽存储器)DRAM、大规模并行高带宽接口和赛灵思最先进的 16nm UltraScale+ All Programmable 芯片完美集成在台积公司 (TSMC) 和赛灵思联合开发的 3D CoWoS 硅中介层 (3D on 3D) 上。赛灵思支持 HBM 的 UltraScale+ FPGA 结合台积公司 (TSMC) CoWoS 硅中介层的高密度高性能互联技术,能实现高达 Tbps 级的带宽性能,相对于独立封装的 FPGA 和 SDRAM 而言,存储器带宽可提升高达 10 倍。将存储器带宽提升 10 倍的赛灵思加速增强型 16nm All Programmable 器件,将能够满足数据中心应用(尤其是云计算)的处理及存储器带宽要求。当日宣布的信息指出:“赛灵思已经在同业界领先的超大规模数据中心客户协作,共同打造优化配置和产品。”

下面披露一些有关 HBM 和台积公司 (TSMC) / 赛灵思联合开发的硅中介层的技术细节

维基百科(Wikipedia)信息显示,最初版 HBM 是 3D 协议栈 DRAM 器件阵列,由 AMD 和 SK Hynix 联合开发,并于 2013 年成为 JEDEC 标准。将单位引脚的存储器传输速率翻了一番的 HBM2 于2016 年 1 月成为 JEDEC 标准。三星仅在几天后就宣布早期量产 HBM2 器件,而 SK Hynix则于 2016 年 3 月对 HBM2 器件进行了演示。所以 HBM 已经非常现实了。

SK Hynix HBM2提供的幻灯片对 HBM1 和 HBM2 进行了比较:

图1:SK Hynix对 HBM1 和 HBM2 进行了对比

HBM 3D存储器协议栈包括多个存储器芯片和可选基础逻辑芯片,它们通过硅通孔(TSV)连接在一起。一个 HBM 2 协议栈的存储器带宽据说超过 1Tbps,多个协议栈可集成到一个器件中。

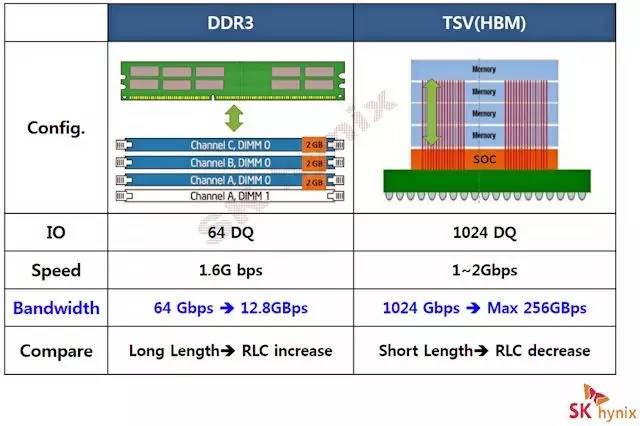

下面这张幻灯片对初始版 HBM 和 DDR3 SDRAM 进行了对比(摘自 2014 年热芯片大会上的 SK Hynix 演示):

图2:HBM 和 DDR3 比较,来自“HBM:适用于高带宽要求处理器的存储器解决方案” Joonyoung Kim和 Younsu Kim 在 2014 年热芯片大会上的演示

您可看到,初始版 HBM 的存储器带宽相对于 DDR3 SDRAM 存储器 Bank 而言提升了 10 多倍。

台积公司 (TSMC) 和赛灵思联合开发的 3D硅中介层技术现已正式称为 CoWoS,并赢得北美 2013 年 SEMI 两项大奖之一。SEMI 是“服务于微电子和纳米电子产业生产供应链的全球产业协会”。

赛灵思基于 CoWoS 硅中介层技术的 16nm 器件是第三代 3D 器件。赛灵思第一代 3D 器件包括一系列基于 28nm 技术的 Virtex-7 FPGA:

Virtex-7 2000T All Programmable 3D IC:全球首款 3D FPGA,单个器件封装,含有5 万个逻辑单元。

Vrtex-7 H580T:全球首款异构 3D FPGA,采用 8 个 28Gbps收发器。

Virtex-7 H870T:全球第二款异构3D FPGA,采用 16 个 28Gbps 收发器,支持 400GE线路卡。

赛灵思第二代 3D 器件包括基于台积公司(TSMC) 20nm 芯片技术、采用 440 万个逻辑单元的 Virtex UltraScale VU440 3D FPGA。

今天宣布的消息称赛灵思将扩展 3D 技术到16nm UltraScale+ 器件系列。您或许已经想到了,由于这是第三代技术,而且已经有两代器件多批次投产供货为基础,因此

CoWoS 是非常牢靠的产品,而且也得到很好的了解和认知。

-

芯片

+关注

关注

456文章

50968浏览量

425048 -

存储器

+关注

关注

38文章

7514浏览量

164036 -

赛灵思

+关注

关注

32文章

1794浏览量

131356

发布评论请先 登录

相关推荐

赛灵思宣布,在其发展蓝图上新增存储器带宽快车道

赛灵思宣布,在其发展蓝图上新增存储器带宽快车道

评论